eHS: Der Nanosekunden-Löser für die Leistungselektronik, dessen Zeit gekommen ist

Leistungselektronik

02 / 25 / 2019

Was ist eHS: The nanosecond power solver?

"Der OPAL-RT electric Hardware Solver (eHS) ist ein leistungsfähiger Fließkomma-Solver ... der es dem Anwender ermöglicht, eine elektrische Schaltung auf einem FPGA automatisch zu simulieren, ohne die mathematischen Gleichungen schreiben zu müssen."

"Es kombiniert die Einfachheit der Erstellung von elektrischen Schaltungsmodellen mit dem neuen OPAL-RT Schematic Editor, der SimPowerSystems Toolbox, PSIM, dem PLECS Blockset oder der NI Multisim software mit den Stärken der OPAL-RT FPGA-basierten Simulatoren, um die Ströme und Spannungen innerhalb der Schaltung in Echtzeit zu lösen, mit einer Abtastzeit von unter 1 µs."

"Der eHS-Solver verwendet eine modifizierte Knotenanalyse. Er löst eine Leitwertmatrix, um die Spannung an jedem Knoten der Schaltung und den Strom in jedem Zweig zu ermitteln. Die Leitwertmatrix der Schaltung wird durch die Implementierung der Pejovic-Methode, die die Schalterimpedanz darstellt, von den Schaltersteuersignalen unabhängig gemacht. Bei dieser Methode wird ein leitender Schalter als Induktivität und ein offener Schalter als Kapazität dargestellt, so dass sich die Leitwertmatrix während der Simulation nicht ändert."

-eHS-Benutzerhandbuch

Kommentar: Luc-André Grégoire, einer der eHS-Entwickler

"eHS-unser elektrische/elektronische Hardware -ist wie alle Simulationswerkzeuge, verwendet aber einen kleineren Zeitschritt, weshalb ein FPGA erforderlich ist. Ein FPGA mkann an sich nicht schneller als eine CPU sein, aber da es für eine bestimmte a einzigen Aufgabe gewidmet ist und näher an der hardware liegt, ist er in der Lage sehr viel schneller als eine CPU es kann. Wir verwenden FPGAs auch zur Erfassung von I/O näher an wo die Berechnung benötigt wirdund dies reduziert elektrische Latenzzeit. eHS ist wie ein unparteiischer Dritter - es ist ein elektronischer Solver, der jedoch auf verschiedenen Arten von hardware ausgeführt werden kann: auf RT-LAB, HYPERSIM oder auf einer Plattform von National Instruments (NI)."

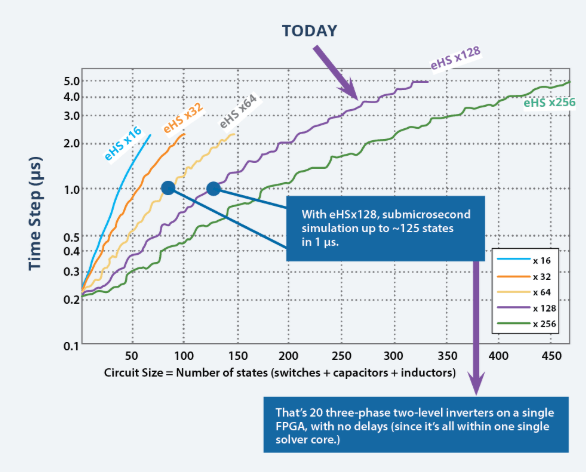

"Nach alledem: Ja, man braucht einen FPGA, weil der Zeitschritt viel kleiner ist. Wenn wir über eHS x128 sprechen, dannbei bedeutet dies eine Simulation im Submikrosekundenbereich bis zu etwa 125 Zuständen in 1 Mikrosekunde. Das ist äquivalent zu 20 dreiphasigen Zwei-Phasen-Wechselrichtern auf einem einzigen FPGA ohne Verzögerungen (da alles in einem einzigen Solver-Kern)-und der Teil 'ohne Verzögerungen' ist natürlich entscheidend, wenn man mit extrem kurzen Zeitschritten arbeiten."

"Im Allgemeinen giltJe mehr Operatoren im Solver vorhanden sind, desto größer und schneller ist der Schaltkreis, der gelöst werden kann. Außerdemje mehr Operatoren im Solver, desto mehr Ressourcen und hardware die dann erforderlich-und damit der von den Ressourcen für den Solver benötigte Fußabdruck ist ebenfalls größer. Wir haben uns die Clusterung dieser FPGAs angesehen: für eine Québec Kunden wurden drei FPGAs in Betracht gezogen, von denen jedes über zwei x128s verfügt. Das bedeutet eine erhebliche Verfügbarkeit von Rechenleistung."

"Vor etwa einem Jahrzehnt haben wir auf der CPU einen Schalter zu einem sehr genauen Zeitpunkt geöffnet und geschlossen, da der Zeitschritt größer war. Da der Zeitschritt größer sein kann als die Zeit, in der man den Schalter öffnen und schließen möchte, haben wir zwischen den Zeitschritten interpoliert, um sicherzustellen, dass wir - obwohl der Zeitschritt viel langsamer ist als die Geschwindigkeit, mit der der Schalter ein- und ausgeschaltet wird - dennoch genaue Ergebnisse erhalten."

"Als wir anfingen, mehr mit FPGA zu arbeiten, dachten wir zunächst: 'Das ist ein viel kleinerer Zeitschritt; wir brauchen nicht mehr zu interpolieren'. Als wir jedoch zu einem kleineren Zeitschritt übergingen, teilte uns Kund:innen mit, dass sie eine viel schnellere Schaltfrequenz verwenden wollten. Eine höhere Schaltfrequenz bedeutete, dass wir bei den Impulsen sehr viel genauer sein mussten. Also haben wir die Interpolation wieder eingeführt, aber jetzt auf FPGA."

"Die Interpolation Werkzeug wurde auf die CPU angewandt, und jetzt verwenden wir dieselbe Art von 'Trick' auf FPGA, aber wir haben es geändert, um ein höher durchführenance als es früher der Fall war erreichenund zur Unterstützung von mehr Dinge. Diese Trick ist ähnlich dem, was unser RT-EVENTS Blocksatz tut, die, der Reihe nach, ist Teil von die CPU-Based Electrical Toolbox im RT-LAB (und bald auch in HYPERSIM). Die vorgesehene Verwendung ist für Wandler, die mit einer Geschwindigkeit von mehr als 20 kHzResonanzwandler - oder eine verbesserte Genauigkeit bei der SwesChing-Veranstaltungs."

"Wenn Sie also einige kaskadierte H-Brücken, die eine Phase sein sollen-verschoben sein sollen, und obwohl sie mit niedriger Frequenz schalten, müssen Sie trotzdem sehr genau auf das Schaltereignis achtens: Dies könnte eine Anwendung sein. Man könnte auch über ultrahochfrequente DC-DC-Wandler sprechen, die GaN (Galliumnitrid) Bauelementen, mit vielleicht 100 kHz Schaltfrequenz - diese eHS-Implementierung ist eine Lösung für einige der deredieser Probleme."

"YSie erwähnten vorhin MMC in HVDC mit gemischten Umrichtern erwähnt. ULetztlich, eHS ist für hochgeschaltetechWandler, und eHS ist sehr gut, weil es ein fixed Matrixlösungr-aber es gibt sind einige Nachteile mit dieser Topologie. Wandler, die mehrere Schalter in Reihe verwenden, sind möglicherweise nicht die besten Kandidaten für eHS, aber mit der von uns vorgeschlagenen Technologie verwenden wir eine Reihe von Schaltern, und schaffen es, auch das zu umgehen."

"Das wirklich Neue daran ist, dass OPAL-RT das erste Unternehmen war, das einen Zeitstempel eingeführt hat.eingeführt hat. Brücke vor etwa 20 Jahren eingeführt hat. Diese Methode ermöglichte die Abtastung eines PWM-Signals mit einer viel höheren Rate als das simulierte Modell. Diese neue Technologie ist nun in unserem neuesten eHS-Solver verfügbar, wo ein PWM-Signal nun mit einer Rate von 200 MHz oder alle 5 ns abgetastet werden kann."

"Die Abtastung der PWM kann bis zu 1 MHz betragen, wobei eine Genauigkeit von 99,5 % erreicht wird. (Zum Vergleich: In früheren Versionen unserer software war die PWM-Frequenz auf 20 kHz begrenzt, um eine ähnliche Genauigkeit zu erreichen). Außerdem kann mit unserem Patent-angemeldeten Modellierungsansatzes jede beliebige 2- oder 3-Pegel-Wandlertopologie (voll-bridge, NPC, Kategorie, Pack-U-Zelle, fliegende Kondensatoren) kann dargestellt werden, auch im blockierten oder unterbrochenen Betrieb."

OPAL-RT Preis für eHS: Prix Innovation PME 2018 @ ADRIQ-RCTi Gala

Wir freuen uns sehr, bekannt zu geben, dass OPAL-RT TECHNOLOGIES gestern Abend auf der ADRIQ-RCTi Gala in Montreal den renommierten Prix Innovation PME 2018 für sein innovatives Produkt eHS erhalten hat, das von unseren innovativsten Kunden auf der ganzen Welt genutzt wird.

OPAL-RT TECHNOLOGIES möchte sich bei allen Entwicklern und Forscher:innen sowie bei allen, die aktiv am Produkt mitgearbeitet haben, herzlich bedanken. Ein besonderes Lob geht an Sébastien Cense, Tarek Ould Bachir, Luc-Andre Gregoire und Christian Dufour, die seit der Entstehung von eHS daran gearbeitet haben.