9 pièges courants Simulation HIL dans la validation des systèmes embarqués et de contrôle

Simulation

03 / 11 / 2026

Principaux enseignements

- N'effectuez les tests HIL qu'après avoir vérifié la synchronisation déterministe, y compris le retard de boucle et la gigue dans le pire des cas sous charge.

- Adaptez la fidélité du modèle de l'installation, les choix du solveur et les imperfections des capteurs et actionneurs à ce à quoi le contrôleur est sensible, et non à ce qui semble convenir sur les graphiques.

- Protégez la crédibilité des tests grâce à des contrôles d'intégration rigoureux, tels que des contrats de signalisation cohérents, des exécutions automatisées et reproductibles, et une traçabilité stricte des versions.

La plupart des échecs des tests HIL ne sont pas dus à une seule erreur majeure. Ils résultent plutôt d'une accumulation de petites incohérences au niveau du timing, de la fidélité du modèle et des détails d'intégration, jusqu'à ce que le banc d'essai devienne peu fiable. Lorsque cela se produit, les équipes réagissent soit en corrigeant de manière excessive, ce qui entraîne des travaux de laboratoire coûteux, soit en livrant le produit avec des lacunes qu'elles pensaient avoir comblées grâce au HIL.

Une Simulation HIL rigoureuse permet d'éviter cette spirale. Il n'est pas nécessaire que tout soit parfait, mais vous devez savoir ce qui doit être précis, ce qui peut être approximatif et comment prouver la différence à l'aide de contrôles répétables. Les pièges ci-dessous se concentrent sur les modes de défaillance qui compromettent le plus souvent la validation des systèmes embarqués et des systèmes de contrôle.

« LesSimulation HIL ne renforcent la confiance que lorsque le timing, les modèles et les interfaces correspondent à votre cible. »

Définissez des objectifs clairs pour les tests HIL avant de procéder au câblage.

Simulation HIL relie votre contrôleur réel à une installation simulée afin que vous puissiez tester le comportement en boucle fermée de manière sûre et reproductible. Le chemin le plus rapide vers des résultats fiables commence par la définition d'objectifs écrits en matière de timing, d'interfaces et de critères d'acceptation, car ces choix déterminent la fidélité du modèle, le matériel d'E/S et la manière dont vous interprétez chaque réussite ou échec.

Définissez ce que signifie « bon » avant que quiconque ne débatte des détails relatifs aux outils ou aux modèles. Cette simple étape empêche les équipes de « régler le système » pour obtenir la réponse qu'elles souhaitent, au lieu de valider le système de contrôle qu'elles prévoient réellement de commercialiser.

- Contrôle des cibles de bande passante et de temps d'échantillonnage

- Plages d'E/S, charges et besoins d'isolation

- Protocoles réseau et tolérances de synchronisation

- Critères de réussite/échec liés aux exigences

- Traçabilité des modèles et des scripts de test

9 Pièges et solutions Simulation HIL

Les problèmes courants liés Simulation HIL peuvent être regroupés en trois thèmes : un timing non déterministe, des modèles qui ne représentent pas ce que « ressent » le contrôleur et des intégrations qui déforment discrètement les signaux. Traitez chaque écueil comme un point de contrôle que vous pouvez vérifier rapidement, avant d'étendre la couverture des tests ou de commencer à rechercher les bogues du contrôleur.

1. Budgets temporels manqués en raison de la taille des pas et de la latence des E/S

Les simulations HIL échouent dans les systèmes embarqués lorsque le timing d'échantillonnage prévu du contrôleur ne correspond pas à la taille de pas du simulateur plus la latence des E/S et du pilote. Pour résoudre ce problème, considérez le timing comme un budget que vous mesurez, et non comme un paramètre que vous supposez. Verrouillez un calendrier à pas fixe, puis confirmez le retard et la gigue de la boucle de bout en bout sous charge.

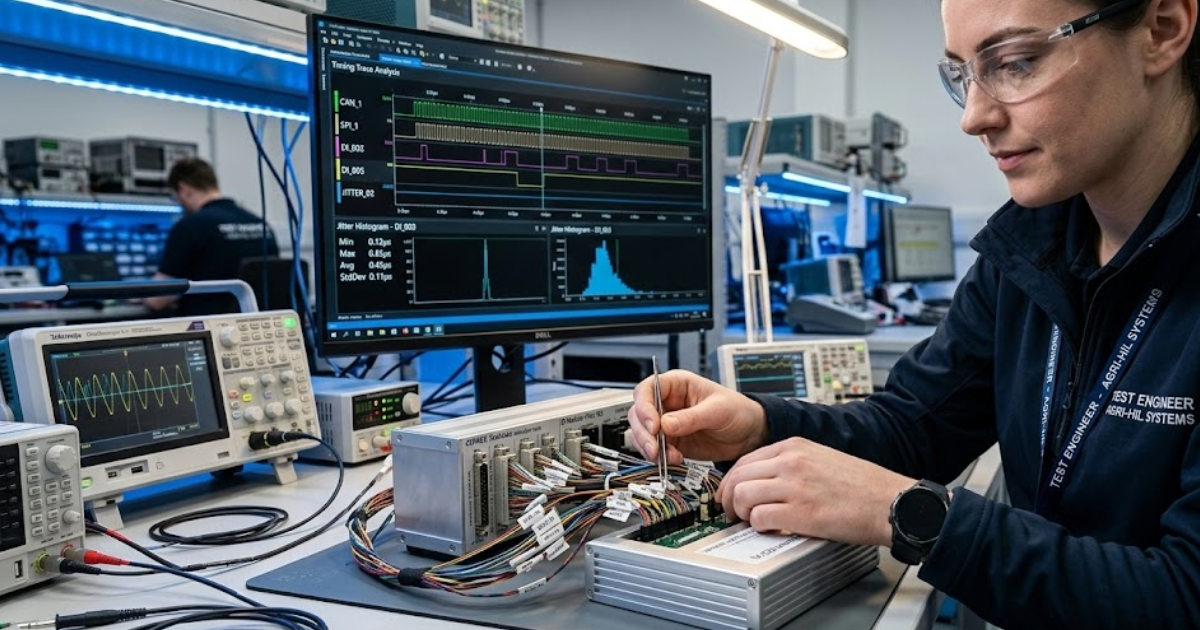

La latence se cache dans des endroits que les équipes négligent : conversions ADC et DAC, piles de protocoles et contention CPU hôte. Une trace d'exécution en temps réel doit montrer le dépassement de pas le plus défavorable et l'âge de mise à jour E/S le plus défavorable, et pas seulement une moyenne. Lorsque vous utilisez des plateformes telles que OPAL-RT, fiez-vous à la planification et à l'instrumentation déterministes pour prouver que le budget de synchronisation reste dans les limites de tolérance de votre contrôleur.

2. Fidélité du modèle de la plante trop faible pour la bande passante du contrôleur

Un modèle de centrale qui semble stable à basse fréquence peut s'avérer inutile à la bande passante du contrôleur, où les retards, les résonances et la saturation déterminent les marges de stabilité. Pour remédier à cela, il convient d'adapter la fidélité du modèle à l'objectif de contrôle, puis de valider la réponse du modèle aux fréquences que le contrôleur va exciter. Conservez les dynamiques à haute fréquence qui affectent la phase et le gain.

La fidélité n'est pas synonyme de complexité. Il est souvent possible de supprimer les détails thermiques ou mécaniques lents tout en conservant la dynamique électrique ou hydraulique rapide qui domine le comportement en boucle fermée. Une vérification pratique consiste à comparer la réponse en fréquence ou la réponse en échelon à une référence fiable, puis à effectuer un test de sensibilité rapide pour voir quels paramètres influencent les résultats positifs ou négatifs.

3. Les choix du solveur et de la discrétisation créent un aliasing et une instabilité.

Les paramètres du solveur peuvent ajouter des effets Énergie, d'amortissement ou de commutation d'alias dans de fausses oscillations. Pour y remédier, sélectionnez des solveurs et une discrétisation qui correspondent à la physique de votre installation et à votre pas en temps réel, puis vérifiez la stabilité numérique à l'aide de cas de contrainte. Un échantillonnage trop lent transforme un contenu haute fréquence légitime en un comportement basse fréquence trompeur.

L'aliasing se manifeste souvent sous la forme d'une « instabilité du contrôleur » qui disparaît sur le banc d'essai. Soyez attentif aux discontinuités, aux événements de commutation et aux retards de transport, puis choisissez des approches de modélisation qui se comportent de manière prévisible dans le cadre d'une exécution à pas fixe. Lorsque l'installation comprend une commutation rapide ou une dynamique rigide, une taille de pas plus petite, des changements de solveur ou des chemins de calcul dédiés seront nécessaires pour maintenir la cohérence de la simulation.

4. Les erreurs de mise à l'échelle du signal et de conditionnement électrique altèrent les mesures.

Un mauvais dimensionnement et un mauvais conditionnement compromettent discrètement les résultats, car le contrôleur continue de fonctionner et vos graphiques semblent toujours plausibles. Corrigez cela à l'aide d'un contrat de signal strict pour chaque canal : unités, dimensionnement, polarité, décalage, filtrage et bruit attendu. Confirmez le contrat à l'aide de vérifications en boucle et de valeurs injectées connues avant d'exécuter des scénarios complexes.

Les détails électriques sont tout aussi importants que les calculs mathématiques. L'impédance d'entrée, l'excitation du capteur, l'isolation, la mise à la terre et les limites en mode commun peuvent fausser les mesures ou déclencher les protections. Si votre banc HIL utilise un conditionnement de signal, considérez-le comme faisant partie de l'installation, car il modifie ce que le contrôleur « voit ». Un enregistrement d'étalonnage clair pour chaque canal vous évitera des jours de débogage par la suite.

5. L'intégration du protocole masque la gigue, la perte de paquets et les réessais.

Les E/S en réseau peuvent sembler fonctionner correctement alors qu'elles sont temporairement défaillantes, en particulier lorsque les tentatives répétées et la mise en mémoire tampon masquent les délais non respectés. Pour remédier à cela, mesurez l'âge, la gigue et la perte des messages dans le pire des cas de charge du bus, puis alignez les hypothèses du contrôleur sur ce que le réseau fournit réellement. Associez chaque message à un horodatage que vous pouvez vérifier.

Les problèmes d'intégration échappent souvent au contrôle de l'équipe, car ils se situent au niveau du micrologiciel de la passerelle, des pilotes ou des configurations des commutateurs. Considérez la configuration du protocole comme faisant partie intégrante de la validation, et non comme une simple formalité. Lorsque vous constatez des défaillances intermittentes, capturez des traces synchronisées des deux côtés de l'interface afin de distinguer les problèmes de synchronisation du contrôleur des problèmes de transmission réseau.

6. Incompatibilités d'interface entre le banc HIL et le matériel cible

Les tests HIL échouent lorsque l'installation simulée se connecte via une interface qui ne correspond pas à celle qui sera utilisée par le système de production. Pour remédier à cela, testez le contrôleur en utilisant les mêmes chemins électriques et protocoles que ceux qu'il utilisera ultérieurement, ou documentez chaque incompatibilité et son impact sur la latence, la résolution et le comportement en cas de défaillance.

Un scénario concret illustre comment cela peut mal tourner : un contrôleur moteur validé sur un pont Ethernet adapté au laboratoire peut passer tous les tests fonctionnels, puis échouer lorsqu'il est transféré vers le bus de production, car les délais d'arbitrage et le décalage des messages modifient le délai effectif de la boucle. Une solution simple consiste à effectuer un test de contrôle précoce du « chemin de production », même si le modèle de l'usine est encore approximatif.

« Une passe n'a d'importance que si vous pouvez la reproduire plus tard. »

7. L'émulation des capteurs et des actionneurs ne tient pas compte des limites, du bruit et des retards.

Les capteurs et actionneurs idéaux donnent une image plus flatteuse des contrôleurs qu'ils ne le sont en réalité. Pour remédier à cela, modélisez les imperfections qui influencent le comportement du contrôle : quantification, biais, dérive, couleur du bruit, zones mortes, limites de débit et délais de transport. Adaptez ces imperfections à celles introduites par votre matériel et votre câblage, et non à des exigences utopiques.

Les limites sont particulièrement importantes lors des transitoires, des défauts et des conditions limites, c'est-à-dire dans les situations où le HIL est censé vous protéger. Si votre modèle d'actionneur ne sature jamais, vous ne verrez pas l'effet d'enroulement de l'intégrateur ni la dynamique de récupération. Si votre modèle de capteur ne présente aucun retard, vous sous-estimerez le déphasage et surestimerez les marges de stabilité. Considérez ces éléments comme des entrées de test, et non comme des détails secondaires.

8. automatisation des tests réduisent la répétabilité et la couverture entre les équipes.

Les exécutions manuelles HIL produisent des résultats que vous ne pouvez ni reproduire, ni comparer, ni défendre. Remédiez à cela grâce à l'exécution de tests scriptés, à la génération aléatoire de bruit, à des conditions initiales déterministes et à la capture automatisée des artefacts. automatisation besoin d'être complexe, mais elle doit permettre de comparer chaque exécution entre les personnes, les jours et les bancs d'essai.

La répétabilité est la différence entre le débogage d'un contrôleur et le débogage du banc d'essai. Enregistrez les journaux, les traces de synchronisation, la configuration du simulateur et les identifiants de compilation du contrôleur à chaque exécution. Lorsqu'une régression apparaît, vous serez en mesure de répondre rapidement à une question fondamentale : le système a-t-il changé ou le test a-t-il changé ?

9. La configuration et la dérive des versions nuisent à la traçabilité des résultats des tests.

La crédibilité des tests HIL s'effondre lorsque les versions des modèles, les ensembles de paramètres, les versions du micrologiciel et les fichiers d'étalonnage dérivent sans traçabilité. Remédiez à cela grâce à un processus de configuration contrôlé qui relie chaque résultat de test aux versions exactes des modèles, des binaires, des chaînes d'outils et des mappages d'E/S. Une réussite n'a de sens que si vous pouvez la reproduire ultérieurement.

La dérive crée également de faux échecs qui font perdre un temps précieux aux ingénieurs seniors. Verrouillez les sources des paramètres, utilisez une nomenclature cohérente et créez une source unique de vérité pour les mappages de canaux et la mise à l'échelle. Lorsque les équipes partagent des plateformes, un contrôle des modifications léger empêche les « petites modifications » de se transformer en semaines de confusion lors de la validation finale.

| Piège | Point à retenir |

|---|---|

| Budgets temporels non respectés en raison de la taille des étapes et de la latence des E/S | Mesurez le retard et la gigue de la boucle, puis appliquez un budget de synchronisation fixe. |

| Fidélité du modèle de plante trop faible pour la bande passante du contrôleur | Maintenir les dynamiques qui affectent la phase et le gain à la bande passante de contrôle. |

| Les choix de solveur et de discrétisation créent un aliasing et une instabilité. | Choisissez des solveurs qui restent stables et évitent l'aliasing sous des pas fixes. |

| Les erreurs de mise à l'échelle du signal et de conditionnement électrique faussent les mesures. | Utilisez un contrat strict en matière d'unités et de mise à l'échelle pour chaque canal d'E/S. |

| L'intégration du protocole masque la gigue, la perte de paquets et les tentatives de renvoi. | Horodater les messages et tester la synchronisation dans les conditions de charge du bus les plus défavorables. |

| Incompatibilités d'interface entre le banc d'essai HIL et le matériel cible | Valider via le chemin d'accès à l'interface de production ou quantifier chaque discordance. |

| L'émulation des capteurs et des actionneurs ne tient pas compte des limites, du bruit et des retards. | Ajouter des imperfections afin que le comportement transitoire et défectueux corresponde au système physique. |

| automatisation des tests réduisent la répétabilité et la couverture entre les équipes. | Automatisez les exécutions et capturez les artefacts afin que les régressions soient vérifiables. |

| La configuration et la dérive des versions compromettent la traçabilité des résultats des tests. | Reliez chaque résultat au modèle, au micrologiciel et aux versions de calibrage exacts. |

Donnez la priorité aux vérifications du timing, de la fidélité et de l'intégration pour accélérer la validation.

Le timing, la fidélité et l'intégration sont les trois seuls critères qui permettent de distinguer systématiquement les tests HIL fiables des tests coûteux et spectaculaires. Commencez par un timing déterministe, puis affinez le modèle de l'installation là où le contrôleur est sensible, et enfin verrouillez les interfaces afin que les signaux aient bien le sens que vous leur attribuez. Cet ordre vous évite de « corriger » le contrôleur pour l'adapter à un équipement défectueux.

Une fois ces bases stabilisées, il devient intéressant d'élargir la couverture des tests, car les échecs renvoient alors au système de contrôle et non à la configuration. Les équipes qui considèrent le HIL comme un processus d'ingénierie rigoureux, y compris celles qui travaillent avec les bancs d'essai OPAL-RT, ont tendance à avancer plus rapidement, car chaque résultat de test reste défendable lorsque les parties prenantes demandent comment il a été obtenu et ce qu'il prouve réellement.

EXata CPS a été spécialement conçu pour des performances en temps réel afin de permettre des études de cyberattaques sur les réseaux électriques à travers la couche du réseau de communication de n'importe quelle taille et se connectant à n'importe quel nombre d'équipements pour des simulations HIL et PHIL. Il s'agit d'une boîte à outils de simulation à événements discrets qui prend en compte toutes les propriétés physiques inhérentes qui affecteront le comportement du réseau (câblé ou sans fil).