## Finite Element Based, FPGA-Implemented Electric Machine Model for Hardware-in-the-Loop (HIL) Simulation

Leveraging Simulation for Hybrid and Electric Powertrain Design in the Automotive, Transportation, and Aerospace Industries

- 1. HIL Simulation by OPAL-RT Introduction & Context

- 2. E-drive simulation Why FPGA?

- 3. PMSM solver on FPGA

- 4. Integration of Maxwell FEA models and eDRIVEsim

- 5. Conclusion

- 6. Q&A

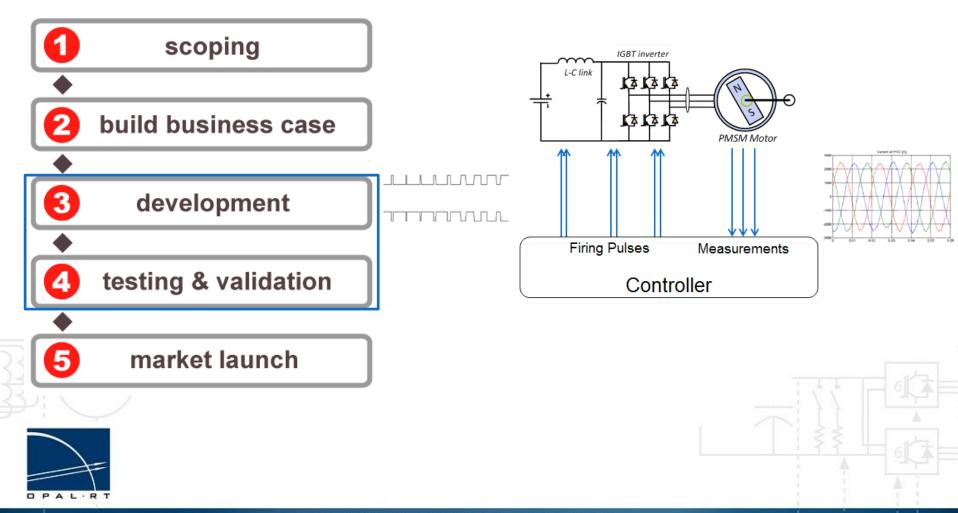

Leveraging Simulation for Hybrid and Electric Powertrain Design in the Automotive, Transportation, and Aerospace Industries We supply **real-time digital simulators** to industry, research labs and educational institutions for hardware-in-the-loop (HIL), rapid control prototyping and accelerated nonrealtime (number crunching) applications

### **OPAL-RT: Turnkey HIL Simulators**

# Hardware, software and integration for real-time simulation and testing

- We program sophisticated solvers and interfaces for real-time applications

- ✓ We design full range I/O signal processing peripherals (modular mapping boxes, FIU, break out boxes)

- ✓ We develop/integrate application models and solutions for various industries (automotive, aerospace, military, power utilities)

### The Challenge of Electric Motor Control Testing

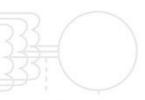

## Faster time to market with parallel development and accelerated test: a proven approach with HIL simulation

### The Challenge of Electric Motor Control Testing

#### Motor control engineers want :

- $\checkmark$  To test the motor controller with non-ideal behavior.

- ✓ To test the motor controller with different points of operation, such a saturated states

- ✓ To insert fault conditions

- To rapidly simulate different types of motors

### The Challenge of Electric Motor Control Testing

#### Managers want to:

- increase test case coverage

- reduce costs

- accelerate time to market

- ✓ By reducing testing time on real dynamometer

- $\checkmark$  By detecting errors at earlier stages of the design

- ✓ Faster improvement of complex control strategies

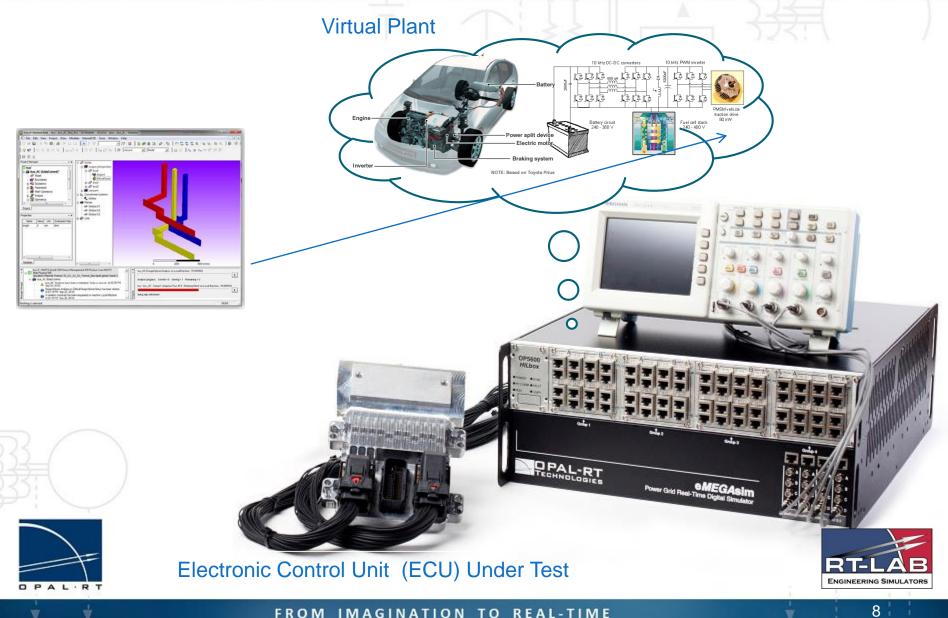

### Creation of a technical link between motor designer and control engineer – HIL model IS the design

### **RT-LAB** for ECU Testing and Validation

### Model-based Design (MBD) & Hardware-in-the-Loop (HIL)

### Why use FPGA?

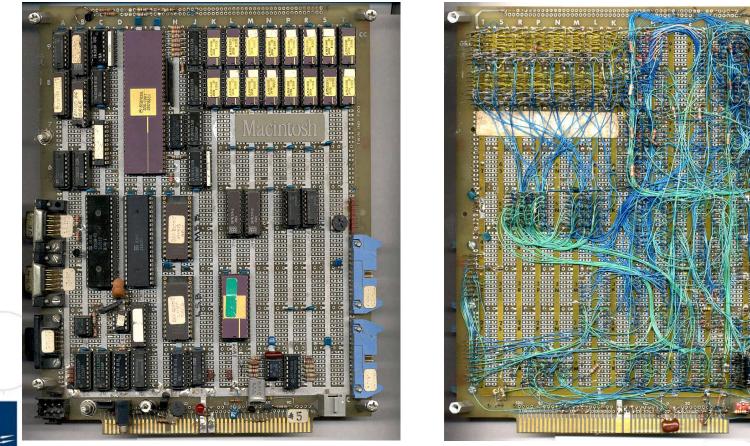

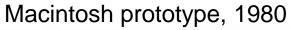

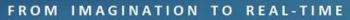

Hang on... First, what's an FPGA??? Well, Before FPGAs, years ago...

### What is an FPGA?

### Now in one integrated cirduit

### What is an FPGA?

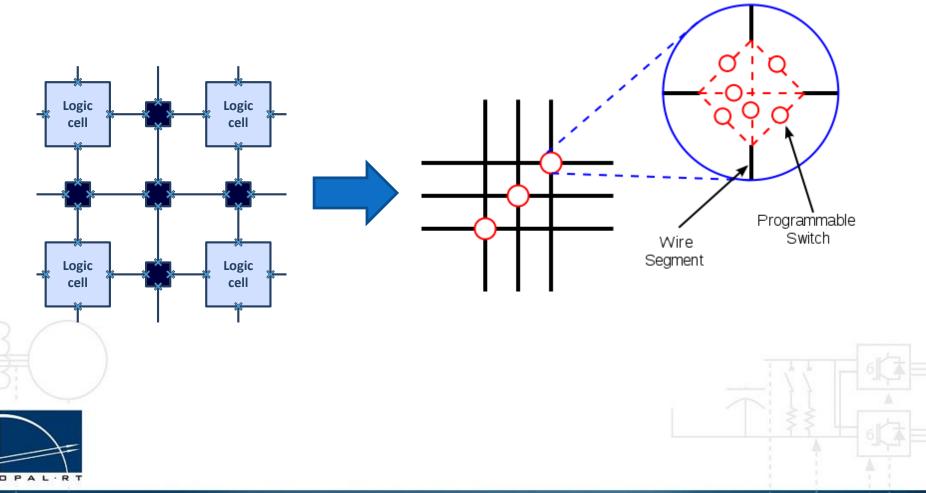

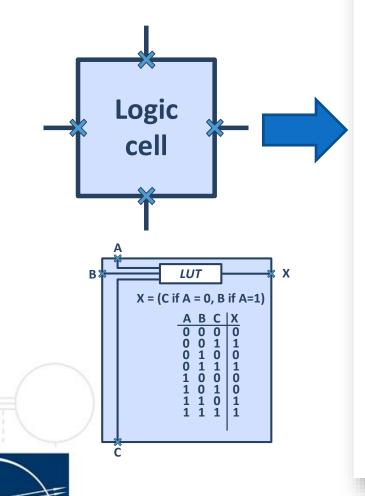

Yeah, I've heard of Integrated Circuits! What's an FPGA!?!? Cells interconnection – Field programmable Gate Array

### What is an FPGA?

PAL·RT

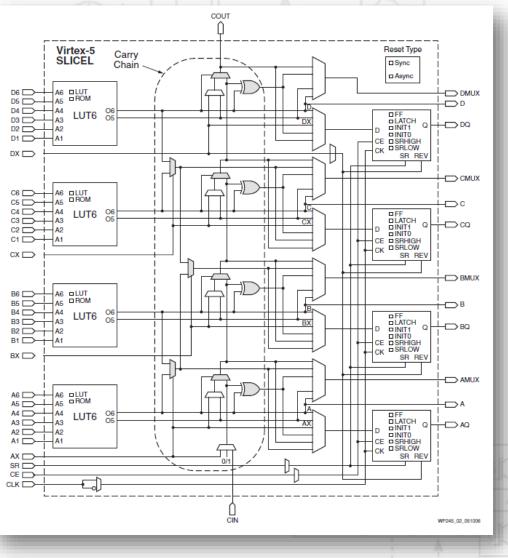

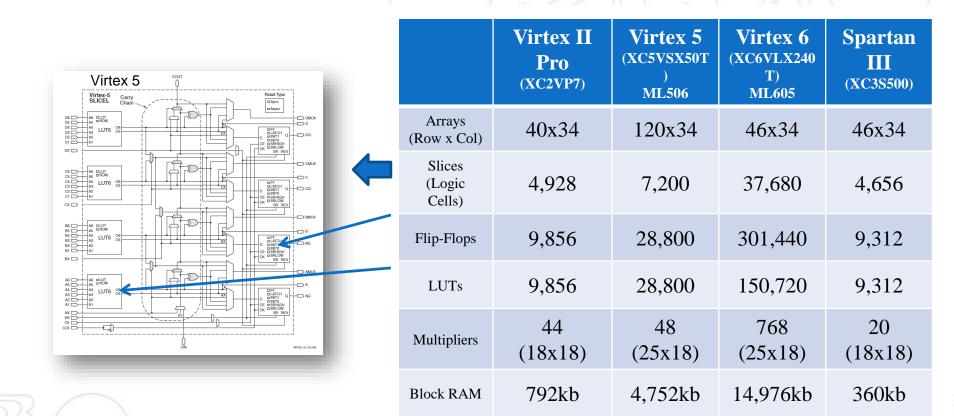

Inside a Virtex 5 Logic Cell

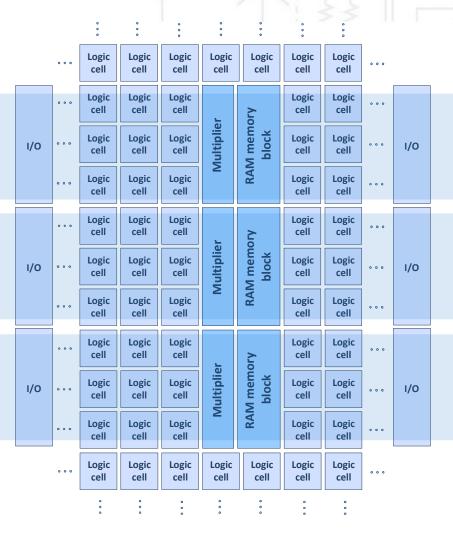

### **FPGA for Parallel Computing**

•OPAL-RT Analog inputs •RT-LAB Digital inputs

•RT-LAB CPU Model

OPAL-RT Analog Outputs

•RT-LAB Digital Outputs

•RT-LAB CPU Model

### Constraints

#### Limited Ressources

- Logic Cells

- > Memory

- > LUTs

- ≻ Etc.

- Might not be possible to route the design

- Propagation delays

- Fixed Point calculation

### FPGAs in Numbers...

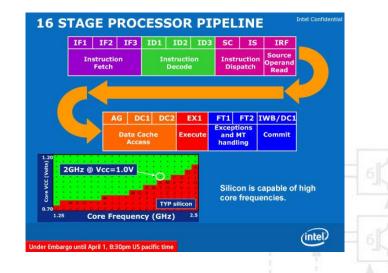

**FPGA**

- Typically 200 MHz clock

- No instruction, everything "executes" at the same time

- Logic blocks are connected together

- Floating point is more challenging (requires a lot of resources)

- Routing & dealing with delays are challenging

- Typically 3.3 GHz clock

- Operations are executed sequentially

- Floating point engine is embedded inside the chip

CPU

### Ok! Why FPGA for HIL then?

#### Advantages compared to CPU-based model processing:

- ✓ Physically near I/O

- ✓ Low latency

- ✓ Parallel signal processing

## Why (not) FPGA?

For most engineers, FPGAs:

$\checkmark$  Are complex to use

HIL turnkey solution fixed vs. floating point

**OPAL-RT's answer**

✓ Lack flexibility

Generic approach to FPGA

✓ Have low fidelity

Implementation of ANSYS Maxwell FEA motor models

## **PMSM Solver on FPGA**

#### **OPAL-RT latest developments:**

✓ CPU equivalent Step Time : 5-20us

Model total Latency: 15-40us

SPATIAL HARMONIC MODEL

Vb

Vb

Vb

Vb

Tm

Tm

Fuvw

collemp

LdLq

> nagTemp EddyLoss heta HysLoss pmsm Vin Euwel din V10.5

Step Time : 100-450ns

$\checkmark$

$\checkmark$

Model total Latency: Below 2.5us

#### **OPAL-RT PMSM FPGA Solver**

### High fidelity modeling + High speed I/Os

### **PMSM Solver on FPGA**

#### **OPAL-RT latest developments:**

- ✓ Upgrade of motor solver to latest FEA software levels

- Solver compatible with PMSM spatial harmonics and VarDQ approach

- ✓ Streamlining of integration steps

- Solver configuration ready in a few clicks with online reconfiguration of I/O mapping

- ✓ Improvement of solver accuracy

Model entirely computed in floating point

## **PMSM Solver on FPGA**

#### Implementation:

- ✓ Export Netlist from ANSYS Maxwell Software

- Precalculation of multiple operating points

- ✓ Import Netlist into RT-LAB environment

Use RT-LAB to build your realtime simulation

- ✓ Ready-for-Realtime

Integrate I/O and any other required application peripherals

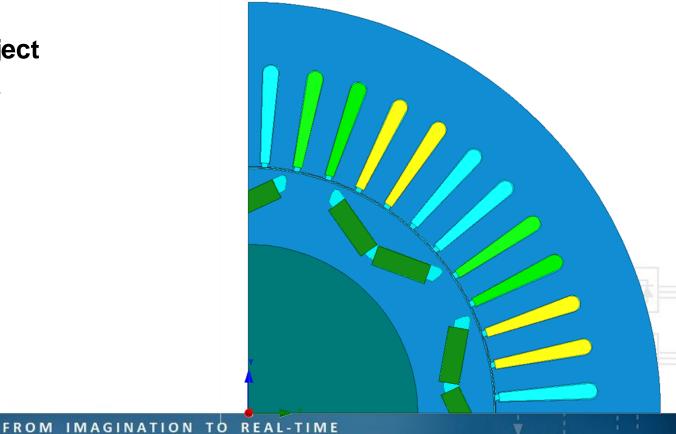

## **OPAL-RT Benchmark Simulation**

### Maxwell 16.0

- OS Linux cluster specifications:

- Total CPUs (cores): 48

- Total hosts (nodes): 4

- Large Scale Distributed Solve Option (LS-DSO)

- Prius motor project

- 17195 variations

- Cores used 48

### Maxwell Setup

Ansoft Maxwell - Prius\_2D\_MSBnd\_v15\_2 - Param\_Sweep - 3D Modeler - [Prius\_2D\_MSBnd\_v15\_2 - Param\_Sweep - Modeler] File Edit View Project Draw Modeler Maxwell 2D Tools Window Help | **2 k?** 8 8 8 8 8 8 8 8 |**0** || 0 | 0 ⊂ 3 ⊂ 0 | 0 0 | 0 ⊂ | 0 ⊂ | Project Manager \* X B B Sheets 🛓 💋 air Prius\_2D\_MSBnd\_v15\_2\* 🛓 🟉 copper Param\_Sweep (Magnetostatic, XY)\* 🖶 🟉 M19\_29G Ø Model M36Z\_20C Boundaries Excitations 🛓 💋 steel\_stainless ⊨ ∼ Lines 🖻 🏶 Parameters Coordinate Systems Hesh Operations 🕒 🕢 🖉 Planes 🖻 🔊 Analysis 🗄 🥔 Lists Setup1 Detimetrics Parametric Setup 1 Results Definitions х Design Settings Material Thresholds Background Matrix Computation Project C Apparent Properties Incremental Unit Evaluated Value Name Value line A 0A De 0 Vm De speed 3000 3000 De 8 De poles 8 ffreq

Save as default speed\*poles/120 200 De -0.3490658503... De -pi/9 lam\*sin(TTheta\*4+beta+shift) -0A De lam\*sin(TTheta\*4-2\*pi/3+beta+shift) 0A De lam\*sin(TTheta\*4+2\*pi/3+beta+shift) -0A De TTheta Theta1+52.5deg 52.5deg De De 0 deg Odeg -30 -30deg De deg ОК Cancel 9\*line 0A De Theta1 0 0deg De deg • Variables 45 90 (mm)

- 0 <u>- X</u>

💽 🔒 🗗 🤸 🛠 🛰 🖽 🖉 🖑 🖑

▼ Model

- 8 ×

W

Ŵ

delta

LA

I\_B

beta

shift

lam

### Maxwell Setup

- Alignment of the initial rotor position is done

- Flux linkage is maximum when theta = 0 and lamp =0

- Parametric sweep table of 17195 rov

- Beta = 0:20:360

- Theta = 0:0.25:45

- lamp = 0:50:200

- Parametric table was run on (LS-DS)

- Results post-processed using Matla

- Final Table:

- Beta = 0:5:360

- Theta = 0:0.25:45

- lamp =

[0,2.5,5,8,11,18,25,37.50,50,75,100,125,150,17 5,20]

Note: Results were post-processed using spline interpolation in Matlab

| weep D | efinitions | Table Gen | ral Calculations Options |   |   |

|--------|------------|-----------|--------------------------|---|---|

| •      | lline      | Theta1    | beta                     | • | A |

| 3867   | 50A        | 16.25deg  | 40deg                    |   |   |

| 3868   | 50A        | 16.5deg   | 40deg                    |   | D |

| 3869   | 50A        | 16.75deg  | 40deg                    |   |   |

| 3870   | 50A        | 17deg     | 40deg                    |   |   |

| 3871   | 50A        | 17.25deg  | 40deg                    |   |   |

| 3872   | 50A        | 17.5deg   | 40deg                    |   |   |

| 3873   | 50A        | 17.75deg  | 40deg                    |   |   |

| 3874   | 50A        | 18deg     | 40deg                    |   |   |

| 3875   | 50A        | 18.25deg  | 40deg                    |   |   |

| 3876   | 50A        | 18.5deg   | 40deg                    |   |   |

| 3877   | 50A        | 18.75deg  | 40deg                    |   |   |

| 3878   | 50A        | 19deg     | 40deg                    |   |   |

| 3879   | 50A        | 19.25deg  | 40deg                    |   |   |

| 3880   | 50A        | 19.5deg   | 40deg                    |   |   |

| 3881   | 50A        | 19.75deg  | 40deg                    |   |   |

| 3882   | 50A        | 20deg     | 40deg                    |   |   |

| 3883   | 50A        | 20.25deg  | 40deg                    | - |   |

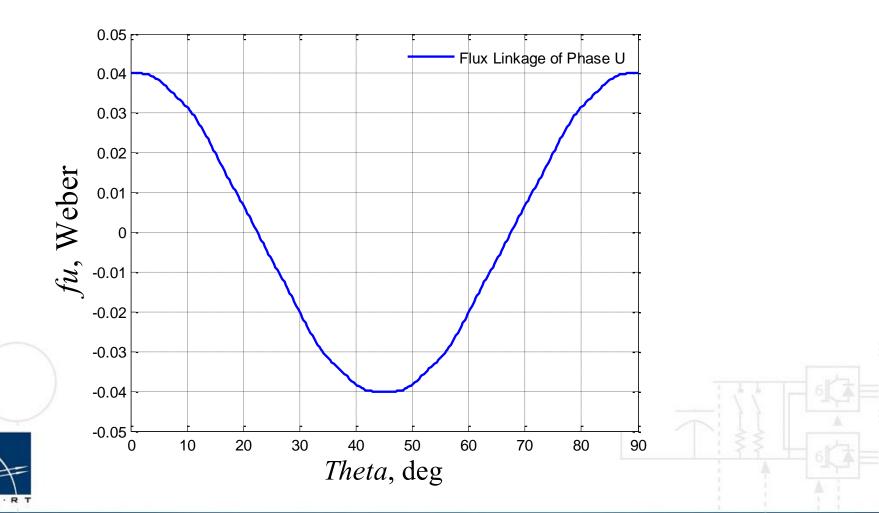

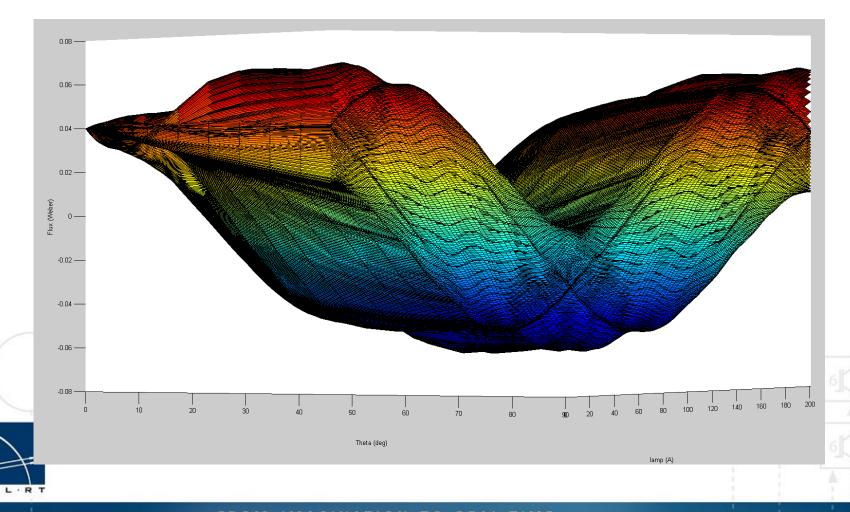

### Results – Flux Linkage

Flux linkage of phase U when Beta = 0 deg and lamp = 0A

FROM IMAGINATION TO REAL-TIME

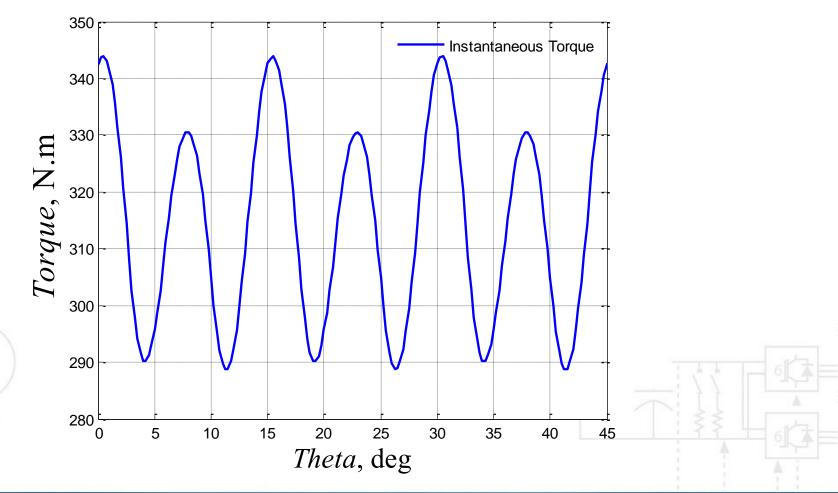

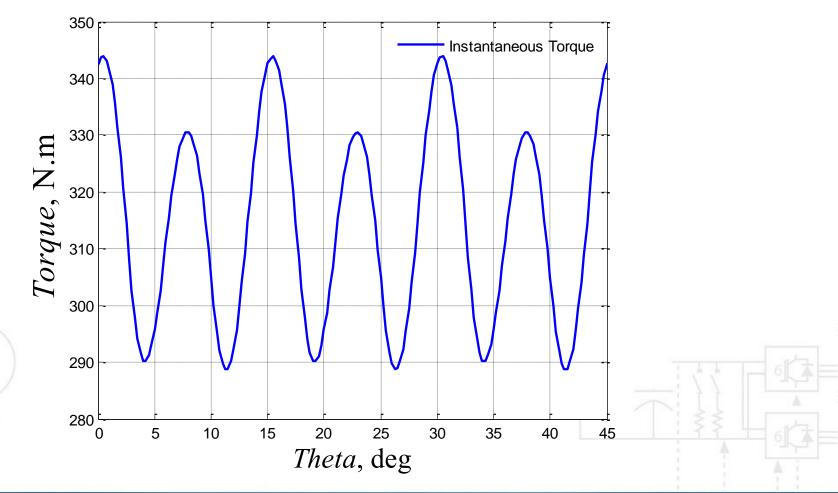

### Results – Instantaneous Torque

Instantaneous torque of phase U when Beta = 45 deg and lamp = 200A

### Results – Instantaneous Torque

Instantaneous torque of phase U when Beta = 45 deg and lamp = 200A

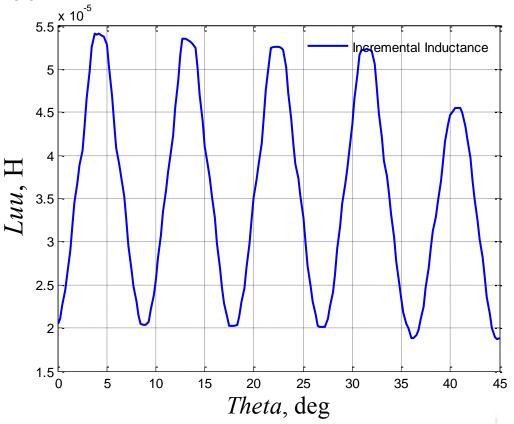

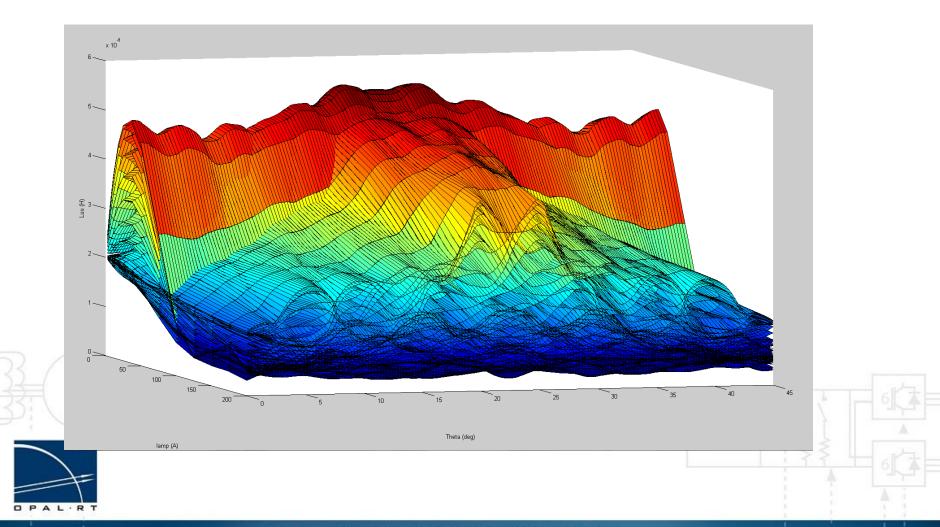

### **Results – Incremental Inductance**

Incremental inductance of phase U when Beta = 45 deg and lamp = 200A

Note: Maxwell also can compute the incremental inductance when lamp = 0

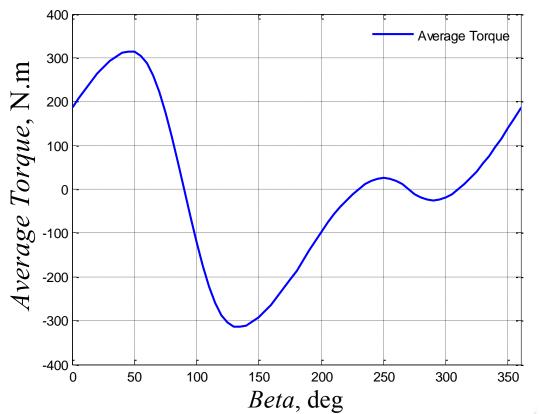

### Results – Average Torque

Average torque of phase U when Beta = 45 deg and lamp = 200A

Note: For motor mode operation, Beta ranges from 0 deg to 90 deg which adheres to the alignment criteria shown in the

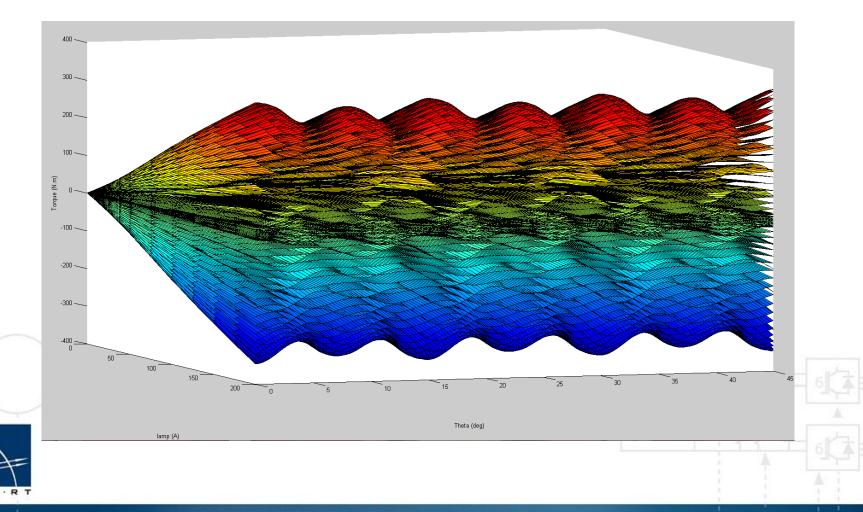

### Results – Instantaneous Torque

#### Instantaneous Torque

### Results – Instantaneous Flux Linkage

#### Instantaneous Flux Linkage

### Results – Instantaneous Flux Linkage

#### Instantaneous Flux Linkage

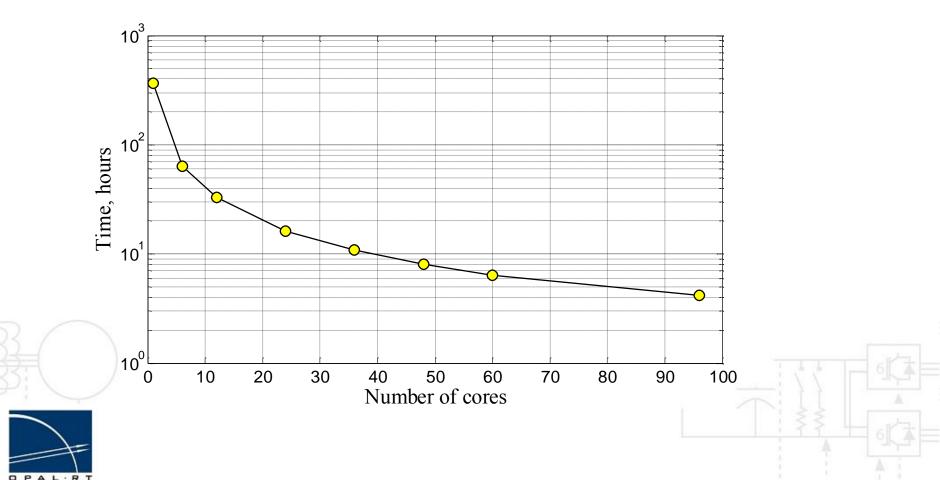

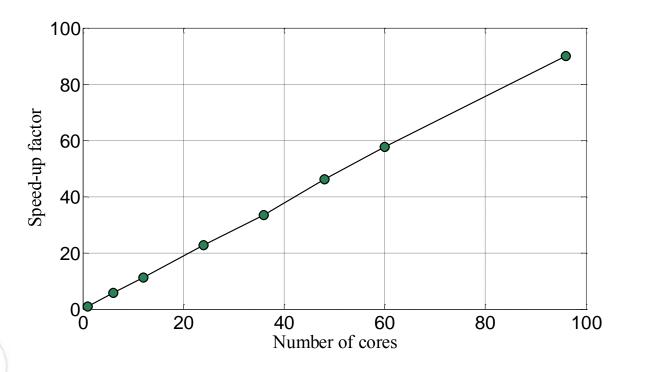

### Speed-up factor and cores utilizations:

| Number<br>of cores | Simulation time<br>(hours) | Speed-up<br>factor | Cores<br>utilization % |

|--------------------|----------------------------|--------------------|------------------------|

| 1                  | 368.3                      | 1                  | 100%                   |

| 6                  | 63.7                       | 5.7                | 95%                    |

| 12                 | 32.9                       | 11.2               | 94%                    |

| 24                 | 16.2                       | 22.8               | 95%                    |

| 36                 | 10.9                       | 33.4               | 94%                    |

| 48                 | 8.0                        | 46.1               | 96%                    |

| 60                 | 6.4                        | 57.6               | 96%                    |

| 96                 | 4.2                        | 90.0               | 94%                    |

### Simulation time in log scale:

### Speed-up factor:

This graph shows that the simulation time is reduced linearly with the increase of number of cores

### Extraction of Results on LS-DSO

Results for all variations extracted using LSDSO extractor with –mergecsv option

All results of the variations are combined in a single CSV file

| Organize 🔻 🛛 Include i | n library 🔻 Share with 👻 Burn New f | older             | :== •             |         |

|------------------------|-------------------------------------|-------------------|-------------------|---------|

| ☆ Favorites            | Name                                | Date modified     | Туре              | Size    |

| Desktop                | Matrix1LGroup1Group1.csv            | 7/31/2013 9:21 AM | Microsoft Excel C | 3,433 K |

| Downloads              | Matrix1LGroup1Group2.csv            | 7/31/2013 9:21 AM | Microsoft Excel C | 3,447 k |

| Recent Places          | Matrix1LGroup1Group3.csv            | 7/31/2013 9:21 AM | Microsoft Excel C | 3,447 1 |

|                        | Matrix1LGroup2Group1.csv            | 7/31/2013 9:21 AM | Microsoft Excel C | 3,447 1 |

| 🔚 Libraries            | Matrix1LGroup2Group2.csv            | 7/31/2013 9:21 AM | Microsoft Excel C | 3,433   |

| Documents              | Matrix1LGroup2Group3.csv            | 7/31/2013 9:21 AM | Microsoft Excel C | 3,447   |

| J Music                | Matrix1LGroup3Group1.csv            | 7/31/2013 9:21 AM | Microsoft Excel C | 3,447   |

| Pictures               | Matrix1LGroup3Group2.csv            | 7/31/2013 9:21 AM | Microsoft Excel C | 3,447   |

| Videos                 | Matrix1LGroup3Group3.csv            | 7/31/2013 9:21 AM | Microsoft Excel C | 3,433   |

|                        | Matrix1MagFluxGroup1.csv            | 7/31/2013 9:21 AM | Microsoft Excel C | 3,403   |

| 🜉 Computer             | Matrix1MagFluxGroup2.csv            | 7/31/2013 9:21 AM | Microsoft Excel C | 3,398   |

| 🚢 OS (C:)              | Matrix1MagFluxGroup3.csv            | 7/31/2013 9:21 AM | Microsoft Excel C | 3,408   |

| 👝 DATAPART1 (D:)       | Torque2Torque.csv                   | 7/31/2013 9:21 AM | Microsoft Excel C | 3,378   |

| 🗣 Network              |                                     |                   |                   |         |

|                        | •                                   |                   |                   |         |

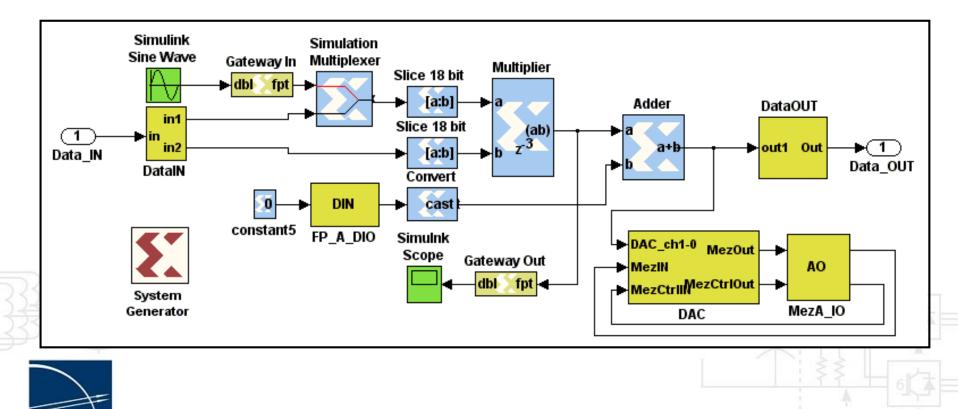

### RT-LAB I/Os are fully programmable with Xilinx System Generator

- Plant model exported from Maxwell, is integrated with I/O & any peripheral plant model components in Simulink to be compiled for real-time.

- Xilinx System Generator is a FPGA Simulink blockset

- No need to know VHDL language

- User can customize the I/O for complex applications

### Conclusion

- ✓ FPGA will soon be the reference for HIL testing

- ✓ High-fidelity HIL model on FPGA is a reality

Large scale parametric analysis of (example) Prius Motor was done to prepare data for OPAL-RT software using ANSYS Maxwell software

- ✓ Motor prototyping is ready

- Enhanced control algorithm validation is now possible on HIL

- ✓ Faster test means lower cost

Motor and controller designer can work closely together – The exported Maxwell model (Design) IS the HIL plant model