# OPAL-RT and PUISSANCE+ Power-Hardware-in-the-Loop Test and Simulation Solution

- More accuracy, reliability and representativeness

- Powerful, high quality equipment manufactured in France and in Canada

- Simulation of algorithms, grids and systems with sources and loads in the loop

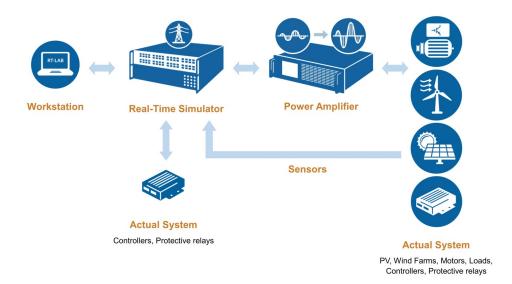

OPAL-RT and PUISSANCE+ have combined their knowledge to supply labs and R&D centers with a unique Power-Hardware -in-the-Loop (PHIL) simulation and test solution. Thanks to tight integration of an OPAL-RT real-time simulation with a PUISSANCE+ linear amplifier, industrial and academic researchers can now test their electrical systems with greater accuracy.

# A Complete and Fully Integrated PHIL Solution

# Simulation with Sources and Loads in the Loop

Combined with a PUISSANCE+ power amplifier, the OPAL-RT simulator provides varying degrees of simulation, from the simple components to very large electrical systems with complex equipment. Thanks to this unique setup, researchers will be able to improve integration and coordination of various sources and electrical loads within a system.

# **Monitoring Interactions**

Closed loop simulation provides data tested in real-time, therefore results are more representative and accurate

because they automatically take into account the various interactions between equipment. Master/slave operations make it possible to interconnect different modular systems.

# Compact, Powerful Equipment

Compact and robust, the amplifier and simulator are at home in laboratories. High performance accuracy, THD, regulation and immunity allow the calibration of Power meters for laboratories, production or maintenance.

### **Typical Applications**

Individual device and interconnected system testing for R&D centers and laboratories:

- Smart Grids and Microgrids

- Integration of Renewables

- Energy Storage Issues

- Electric Vehicle Loads

## **Technical Specifications**

#### **OPAL-RT Real-Time Simulators**

From compact entry-level systems to high-end and FPGA-based simulators

- From 4 to 12 CPU cores @3.4GHz

- FPGA Kintex 7, Spartan 3, Virtex 6 & 7

- Up to 256 I/O lines (analog and/or digital)

- Model sampling period from 1 s (1 Hz) to 200 ns (5 MHz)

- Up to 20,000 3-phases buses simulated (phasor mode)

- Embedded hard-drive for real-time data logging

#### **PUISSANCE+ Power Amplifiers**

4 modules main frame (up to 64 modules)

- AC current source up to 2000A/200KVA

- AC voltage source up to 600V/360KVA

- DC LOAD: 125W/250KW 0V to 600V

- DC power supply: from 0 to 600V-200W/300KW

- 2Q DC power supply up to 125W/10KW

- AC load: 125VA/200KVA

- DC...50KHz

- Harmonic generation 40...300KHz

- Programmable phase angle, distortion, ramp, peak level, ripple, noise

#### **Success Stories**

EDF, the major French utility, built Concept Grid, an experimental platform intended to anticipate and follow the evolution of electrical systems. To make it even more representative of real distribution grids, EDF constructed a residential district with model homes, each with real equipment or equipment representing future use, such as smart counters, remote controlled appliances, micro wind turbines or even photovoltaic panels. Wholly dedicated to "smart" systems, this experimental platform is equipped with a simulator coupled with a power amplifier.

The French National Institute of Solar Energy (INES) is a research center dedicated to research, innovation and training in the area of photovoltaic and thermal solar energy. Its research activities cover the entire sector, from materials to incorporating solar energy in buildings, as well as mobility, storage and network management. The INES has its own demonstration platform, micro-grid and large-scale simulation systems.

#### **OPAL-RT EUROPE**

196 rue Houdan, 92330 Sceaux, France +33 (0)1 41 75 40 80 info@opal-rt.com www.opal-rt.com

#### **PUISSANCE+**

500 avenue du Danemark, Zl Albasud, 82000 Montauban, France +33 (0)5 63 02 14 21 contact@puissanceplus.com www.puissanceplus.com