核心要点

- 仿真 您的硬件在环(HIL)目标能够容忍较大的固定步长和稳定的I/O延迟,且通过标准侧重于控制逻辑和平均电气行为仿真 ,请选择CPU仿真 。

- 仿真 测试依赖于开关沿、微秒级定时以及确定性保护响应仿真 ,必须仿真 FPGA仿真 ,因为CPU在最坏负载条件下无法保证这些特性。

- 通过可量化的接受标准锁定您的选择,包括步长、超限余量和端到端I/O延迟,然后将模型保真度与您必须确认的故障相匹配。

仿真 微秒级计时成为硬性测试要求仿真 ,请选择CPU仿真 模式。

高速电机驱动测试会在模拟器平滑处理市场活动 触发保护机制、饱和电流传感器或破坏快速电流回路稳定性的市场活动 时中断。 电动机 约占总能耗的,因此确保驱动行为正确的重要性远超单个控制器项目。

CPU与FPGA仿真 规格参数的比拼。

实用分离器在于:在所需步长下实现时间确定性,同时通过硬件在回路(HIL)闭环时保持可预测的I/O延迟。从测试目标出发,制定验收标准,并选择每次都能满足这些标准的最简计算方案。

根据电机驱动器HIL测试目标选择CPU或FPGA

仿真 主要区别仿真 它们处理实时执行中的时间和并发性。CPU虽能高速运行顺序代码,但仍需应对调度抖动和步长限制。而FPGA能以确定性时序并行执行多项操作,这在测试依赖于亚周期切换行为时尤为重要。

基于CPU的HIL最适合用于验证控制逻辑、启动序列、故障状态机以及依赖平均电气行为的监控。基于FPGA的HIL最适合在必须精确呈现开关沿、死区效应和快速保护路径时使用,避免将其隐藏在较大的时间步长内。当仅需对功率级实现微秒级分辨率时,混合方案同样效果显著。

| 在硬件在环测试中必须捕获的内容 | 通常适用的计算选择 |

| 在毫秒和数十微秒时间尺度上控制行为。 | CPU仿真 固定步长求解器。 |

| 与PWM沿相关的开关纹波和瞬态电流。 | 仿真 微秒为步长。 |

| 闭环保护系统具有极低且可重复的I/O延迟。 | 基于FPGA的I/O与工厂划分。 |

| 大型工厂场景中,模型尺寸比切换细节更为重要。 | 仿真 简化功率级模型。 |

| 混合保真度:逆变器细节清晰,机械结构仍显粗糙。 | 混合CPU与FPGA在子系统间进行划分。 |

了解导致基于CPU的仿真中断的时间限制

当所需的固定时间步长变得过小时仿真 ——此时求解器和I/O任务无法在下一时钟周期前完成。延误的截止时间会表现为超时、抖动或强制步长增大,这些伪像将破坏您用于评估控制器质量的测量数据。

当将开关模型、传感器滤波和接口处理堆叠在同一循环中时,时序风险随之上升。更快的CPU虽能缓解问题,但确定性仍取决于最坏情况下的执行时间,而非平均性能。若线程争夺内存资源,或I/O处理在关键时刻占用周期,多核架构同样可能带来意外。

实际可接受性始于严格的时间预算:包含系统求解时间、I/O采样时间、日志记录时间及安全裕度。若测试要求单个位数的微秒级步长且需与物理控制器紧密闭环,纯CPU仿真方案将陷入与裕度持续博弈的困境。当所需步长放宽时,仿真 高效且更易于迭代。

仿真 开关级电力电子器件的保真度

当开关级保真度是测试重点而非可忽略的细节时 仿真不可或缺。确定性并行执行使您能够以极小的时间步长呈现器件级行为、PWM时序及快速保护路径。这种保真度确保控制器能清晰感知故障、纹波及换向效应。

更高的开关频率会促使你采用这种方案,因为在每个控制周期内电气系统的变化幅度更大。宽禁带半导体可支持高达 比硅器件高出10倍 ,这使得任何关注电流纹波、dv/dt相关效应或周期性保护的测试都面临更严格的时序要求。

FPGA工作确实增加了限制条件。模型开发通常采用定点运算、精细缩放,并明确划分必须以微秒级运行的部分与可放缓执行的部分。OPAL-RT等平台常被用于清晰分离CPU与FPGA的工作负载,从而确保快速功率级定时具有确定性,同时将监控逻辑和更庞大的系统上下文保留在CPU上。

将求解器的步长与PWM频率和控制回路匹配

步长选择应从测试必须观测的最快现象开始,然后回溯到控制器将如何处理该信息。若仅需平均扭矩和速度响应,可采用较大步长并简化切换逻辑。若需逐周期行为响应,则步长必须足够小以确保其完整性。

具体核查有助于理解:20 kHz PWM周期为50 µs,而电流环路可在其上运行数千赫兹。若采用25 µs系统阶跃响应,每个开关周期仅能捕捉两个数据点,这将导致开关纹波模糊化,并可能掩盖触发保护的峰值电流。 采用1微秒至2微秒的阶跃信号,能更充分解析开关周期,使峰值行为同时可被软件和硬件故障逻辑识别。

求解器选择和划分方案的重要性不亚于原始步长。平均逆变器模型适用于控制调谐和效率研究,但无法验证栅极时序、死区时间补偿或周期精确的去饱和路径。开关模型还要求将采样、量化和延迟作为测试的核心环节,而非事后考虑。

检查电机驱动测试的I/O延迟和接口需求

在通过硬件在环(HIL)实现闭环控制时,I/O延迟是系统固有特性。控制器根据测得的电流、电压和位置信号作出响应,并期望这些信号以稳定的延迟到达。若延迟出现波动,调试结果将无法延续,保护功能的验证也将失去可信度。

从控制器实际使用的接口开始:PWM输出、栅极控制信号、电流反馈、直流母线检测、编码器或旋转变压器位置信号以及故障线。每条信号路径都会增加转换时间、缓冲和调度开销,其总和必须控制在环路预算范围内。确定性延迟往往比最小延迟更重要,因为稳定的延迟可通过补偿实现,而抖动则会转化为相位噪声。

硬件分区不仅是计算工具,更是时序工具。当需要可重复的微秒级响应时,高速I/O捕获与生成功能与FPGA执行天然契合。若接口速度较慢、控制周期较长,或主要目标是功能行为而非沿边时序,则更适合采用CPU执行。

避免常见的选择错误,并设定明确的验收标准

常见错误是优先选择计算方案,其次才考虑测试意图。当团队将平均性能等同于确定性性能,或要求大型工厂模型以微秒步长运行时,纯CPU架构就会失败。当团队耗费精力在测试计划从未用到的切换细节上时,纯FPGA架构也会失败。

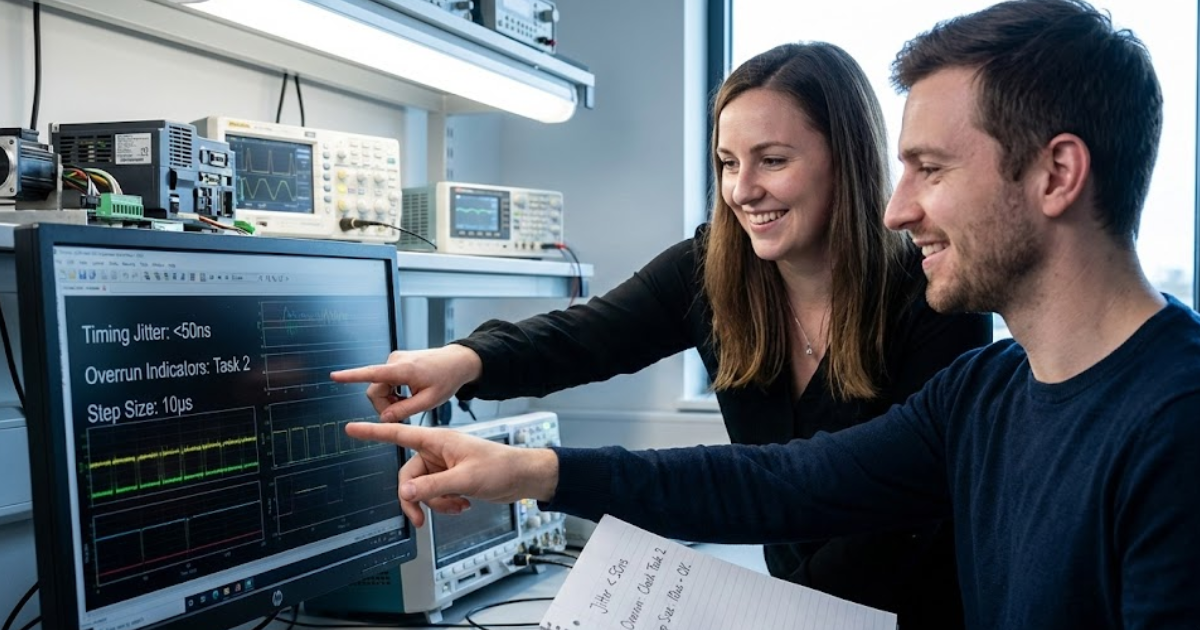

制定可在调试期间量化的验收标准,并据此进行系统调试。确保标准与控制器实际采样及保护路径相关联,而非基于模拟器的通用性能宣称。将模型细节与必须确认的故障案例对齐,并将其他所有内容精简至仅支持这些案例的必要程度。

- 在最坏故障场景下,您的固定时间步长仍将保持稳定。

- 端到端I/O延迟将在您的循环预算范围内具有可重复性。

- 切换细节仅在测试需要时才会显示。

- 超时和抖动将被记录并视为测试失败。

- 模型范围将匹配签核问题,而非团队偏好。

当你将时序和延迟视为工程要求时,CPU与FPGA仿真 争议焦点。

在HIL验证过程中,当CPU能满足步长要求并确保I/O稳定性时,应选择CPU;当开关级动态响应和确定性响应属于通过标准时,则应选择FPGA。在OPAL-RT平台上严格遵循此原则的团队,往往能在实验室中更快推进工作——因为模拟器的选择基于可量化的行为表现,而非主观臆断。

EXata CPS 专为实时性能而设计,可通过任何规模的通信网络层和连接任何数量的设备进行 HIL 和 PHIL 仿真,从而对电力系统的网络攻击进行研究。这是一个离散事件仿真 工具包,考虑了所有会影响网络(有线或无线)行为的固有物理属性。