Verwaltung hochfrequenter Schaltvorgänge in der Echtzeit-EMT-Simulation

Industrieanwendungen, Simulation

31. März 2026

Wichtigste Erkenntnisse

- Durch das Hochfrequenzschalten ist die Wahl der Architektur wichtiger als die des Solvers; daher sollten schnelle Wandlerabschnitte auf dem FPGA angesiedelt werden, sobald Timing-Fehler das Verhalten beeinflussen.

- CPU-Ressourcen sind für große elektrische Strukturen und langsamere Teilsysteme nach wie vor wertvoll, insbesondere wenn Partitionierung und die Ausführung mit unterschiedlichen Geschwindigkeiten sorgfältig gehandhabt werden.

- Die hybride Ausführung funktioniert am besten, wenn Sie jedes Teilsystem der hardware zuordnen, hardware hinsichtlich Zeitanforderungen, I/O und Validierungsziel am besten dazu passt.

Die Bewältigung hochfrequenter Schaltvorgänge in Echtzeit-EMT-Simulationen läuft auf eine schwierige technische Entscheidung hinaus: Das schnellste Wandlerverhalten gehört auf hardware, während der Rest des Systems nur dann auf die CPU verlagert werden sollte, wenn das Zeitschrittbudget ausreichend groß ist. Diese Entscheidung ist heute umso wichtiger, da die Kapazität aus erneuerbaren Energien im Jahr 2023 auf fast 510 GW gestiegen ist, was bedeutet, dass immer mehr umrichterbasierte Geräte in Netze, Antriebe, Speichersysteme und Prüfstände Einzug halten.

Sie können große EMT-Modelle weiterhin in Echtzeit ausführen, allerdings erst, wenn Sie aufhören, jedes Teilsystem so zu behandeln, als benötige es dieselbe numerische Bearbeitung. Schnelle Schaltvorgänge, eine hohe Anzahl an Wandlern und Tests mit Regelkreisen Tests generische Modellstrukturen Tests . Der Harvest-Fall zeigt dies deutlich auf den Seiten 2 bis 5, wo eine hohe Schalteranzahl, hohe Anforderungen an das Timing und eine gemischte Ausführung auf CPU und FPGA als praktische Grenzen und nicht als abstrakte Modellierungsdetails behandelt werden.

Die Leistung von Echtzeitsimulationen hängt von der Wahl der Rechnerarchitektur ab

Die Echtzeit-Leistung von EMT hängt in erster Linie von der Architektur und erst in zweiter Linie von den Modelldetails ab. Sie werden Termine verpassen, wenn der Solver, der Zeitschritt und hardware nicht auf das Schaltverhalten abgestimmt sind, das Sie nachbilden möchten.

Die Wahl der Architektur sollte als Frage des richtigen Zeitpunkts betrachtet werden, nicht als Frage software . Eine CPU eignet sich hervorragend, solange die Ereignisdichte moderat bleibt und die Partitionierung klar ist. Sobald sich Switch-Ereignisse über viele Submodule hinweg häufen und die Behandlung von Totzeiten eine Rolle spielt, wird die Ausführungsplattform zum wichtigsten Modellierungsparameter. Teams, die dies ignorieren, verbringen in der Regel Wochen damit, einen Solver zu optimieren, der für die Arbeitslast von vornherein ungeeignet war.

CPU-basierte Simulation eignet sich für große Systemmodelle mit moderater Schaltdynamik

CPU-basierte EMT eignet sich am besten, wenn Breite wichtiger ist als Schaltgranularität. Große elektrische Netzwerke, Transformatoren, passive Komponenten und Wandlerabschnitte mit langsameren Schaltvorgängen lassen sich in der Regel gut mit CPU-Lösern berechnen.

In einer Fallstudiewar auf der Gleichrichterseite kein Hochfrequenzschalten erforderlich, sodass ein Zeitschritt im Bereich von einigen zehn Mikrosekunden ausreichte. Der CPU-Löser spielte dennoch eine wichtige Rolle, da er mehr als zwanzig Wandler von einem Mehrwicklungstransformator entkoppelte und das Modell innerhalb der Echtzeitgrenzen hielt, ohne dass ein weiteres FPGA hinzugefügt werden musste.

Das ist die richtige Art und Weise, CPU-Ressourcen zu nutzen. Man weist sie den Teilen des Modells zu, die zwar numerisch umfangreich, aber nicht ereignisreich sind. Außerdem gewinnt man dadurch Flexibilität für umfassendere Netzstudien, Fehlerkonfigurationen und Anlagenerweiterungen. Probleme treten auf, wenn man die CPU dazu auffordert, jeden Gatterübergang, jedes Totzeitintervall und jedes phasenverschobene Schaltvorgang in einem Umrichterstapel zu reproduzieren, der eindeutig eine viel feinere Auflösung erfordert.

Die FPGA-basierte Simulation unterstützt Zeitschritte im Nanosekundenbereich und Modelle mit hoher Schaltfrequenz

Die Ausführung auf einem FPGA ist die praktische Lösung, wenn die Schaltdetails das eigentliche Ziel sind und nicht nur ein Nebeneffekt. Sie bietet ein deterministisches Timing und sehr kleine Zeitschritte, die CPUs unter Echtzeit-Anforderungen nicht einhalten können.

Auf Seite 4 des Dokuments heißt es, dass die FPGA-basierte Power-Electronics-Toolbox Schaltfrequenzen über 200 kHz und Zeitschritte im Nanosekundenbereich unterstützt. Dies ist entscheidend für schnelle Wandlerzweige, detailliertes PWM-Verhalten und Wechselwirkungen zwischen Bauteilen, die bei einer Vergrößerung des Zeitschritts nicht mehr erkennbar sind. Ein kaskadierter H-Brücken-Wechselrichter oder ein Hochgeschwindigkeits-SiC-Wandler ist ein gutes Beispiel Vorteil , da Vorteil den elektrischen Ausgangswert Vorteil beeinflusst.

Auch aktuelle Laboruntersuchungen spiegeln diesen Druck seitens hardware wider. Eine NREL-Studie stellt fest, dass die meisten Hochleistungswandler mit einer Schaltfrequenz von 10 kHz bis 50 kHz arbeiten, was bereits eine starke Belastung für das Timing des Echtzeit-Lösers darstellt, noch bevor man mehrstufige Phasenverschiebungen oder Fehlerlogik hinzufügt.

„Die Steuerung hochfrequenter Schaltvorgänge in einer Echtzeit-EMT-Simulation läuft auf eine schwierige technische Entscheidung hinaus: Das schnellste Wandlerverhalten gehört auf hardware FPGA hardware, während der Rest des Systems nur dann auf die CPU verlagert werden sollte, wenn das Zeitschrittbudget ausreichend groß ist.“

Das Schaltverhalten der Leistungselektronik entscheidet oft darüber, wann ein FPGA erforderlich wird

Nicht allein die Modellgröße, sondern das Schaltverhalten gibt Aufschluss darüber, wann ein FPGA erforderlich wird. Der Hauptgrund sind dichte, sich wiederholende Schaltvorgänge, deren Zeitabweichungen die Regelcharakteristik, Verluste, Oberschwingungen oder die Schutzlogik beeinflussen.

Als Beispielschaltete jedes einzelne Vollbrücken-Submodul mit 500 Hz bis 1000 Hz, doch die Phasenverschiebung über mehrere Stufen hinweg und die PWM-Totzeit erhöhten die effektive Schaltfrequenz pro Phase auf bis zu 10 kHz. Das ist genau die Art von Situation, in der ein Modell auf dem Papier einfach aussehen mag, in der Praxis jedoch schwierig umzusetzen ist.

Sie sollten auf drei Warnzeichen achten. Erstens beginnen kleine Timing-Fehler bei den Gatterzeiten, die Wellenform zu verzerren. Zweitens schalten mehrere Wandlerzellen versetzt, was die Ereignisrate vervielfacht. Drittens sind Schutz- und Steuerungsfunktionen darauf angewiesen, dass diese Ereignisse ohne Jitter reproduziert werden. Sobald diese Anzeichen auftreten, ist ein FPGA nicht mehr nur eine Option zur Optimierung. Es wird zum einzigen zuverlässigen Weg, um das Timing korrekt zu halten.

Modellierungsstrategien, die die Ausführung auf CPU und FPGA effektiv kombinieren

Die besten Echtzeit-EMT-Systeme verlangen nicht von Kategorie Prozessor, alles Kategorie erledigen. Sie teilen das Modell so auf, dass jeder Prozessor die physikalischen Berechnungen übernimmt, die er innerhalb seines eigenen Zeitbudgets präzise lösen kann.

Ein Mittelspannungsantrieb ist ein anschauliches Beispiel dafür. Die Wechselrichterseite mit ihren zahlreichen Schaltvorgängen und strengen Anforderungen an die Totzeit gehört auf den FPGA. Der Gleichrichter, die Transformatorankopplung und die langsamere Netzdynamik können auf der CPU verbleiben, da ihre Rechenanforderungen im Mikrosekundenbereich liegen. Genau diese Aufteilung zeigt sich in der Studie: Der FPGA übernimmt den umwandlerintensiven Teil, während die CPU die größere, aber langsamere elektrische Struktur abdeckt.

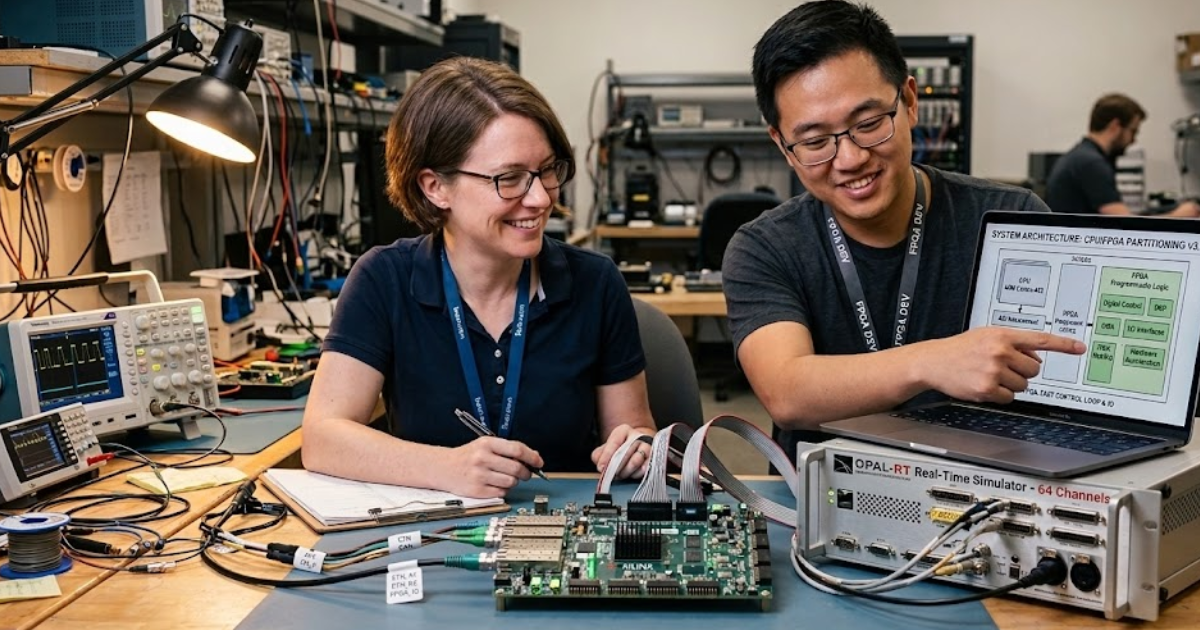

Eine Plattform wie OPAL-RT ist hier von Bedeutung, da es bei dem Arbeitsablauf nicht nur um reine Geschwindigkeit geht. Man benötigt I/O saubere I/O , eine synchronisierte Ausführung und eine praktikable Möglichkeit, das Modell zu erweitern, wenn die Anzahl der Konverter steigt. Eine schlechte Partitionierung verursacht mehr Probleme bei der Schnittstelle als sie für den Solver bringt; daher sollte die Grenze zwischen CPU und FPGA dem Schaltverhalten folgen und nicht organisatorischen Gewohnheiten.

| Die Situation, die Sie modellieren | Eine Ausführungsoption, die die Echtzeit-Glaubwürdigkeit gewährleistet | Hauptgrund dafür, dass diese Entscheidung Bestand hat |

| Ein großes Netz mit Leitungen, Transformatoren und mäßiger Umrichteraktivität | Halten Sie den Großteil der Anlage mit einem gröberen festen Schritt auf der CPU | Die Switching-Details sind so begrenzt, dass die CPU ihre Ressourcen für die Skalierung und Kopplung des Netzwerks einsetzen kann |

| Ein Wandlerzweig mit hoher PWM-Frequenz und hoher Empfindlichkeit gegenüber kurzen Totzeiten | Verlege diesen Konverterteil in die FPGA-Ausführung | Die Zeitauflösung muss bei einem wesentlich kleineren Schritt als dem, den eine CPU normalerweise bewältigt, deterministisch bleiben |

| Ein mehrstufiger Antrieb mit versetzter Schaltung über viele Zellen hinweg | Die schnellen Inverterzellen auf den FPGA aufteilen und die langsameren Hilfsblöcke auf der CPU belassen | Die Ereignisdichte steigt schneller an als die Modellgröße, sodass bei der gemischten Ausführung keine hohe Auflösung für langsame Teilsysteme verschwendet wird |

| Ein Regler-Prüfstand mit Encoder- und Motorrückführung im Regelkreis | Die schnelle Anlagenschnittstelle auf dem FPGA belassen und langsamere Anlagenteile auf der CPU ausführen | Timing-Fehler im geschlossenen Regelkreis treten schnell auf, wenn Sensor- und Schaltsignale verzögert sind oder Jitter aufweisen |

| Ein kostengünstiges Laborsystem, das dennoch eine breite Pflanzenabdeckung erfordert | Reservieren Sie FPGA-Ressourcen nur für die Bereiche, die sie tatsächlich benötigen | Durch gezielte Platzierung wird die Klangtreue dort gewährleistet, wo es darauf ankommt, und es wird vermieden, für eine präzise zeitliche Abstimmung über das gesamte Modell hinweg zu bezahlen |

Kosten, Skalierbarkeit und Integrationsbeschränkungen, die architektonische Entscheidungen beeinflussen

Architekturentscheidungen sind zwar technischer Natur, werden aber dennoch von Budget- und Laborbeschränkungen beeinflusst. Das Ziel besteht nicht darin, alles auf dem FPGA unterzubringen. Das Ziel ist es, Feinabstimmungen nur dort vorzunehmen, wo sie das Testergebnis beeinflussen.

Die hardware auf Seite 3 veranschaulichen, wie dies in der Praxis funktioniert. Der dort beschriebene Simulator unterstützt 3-phasige Vollbrückentopologien mit 8 bis 13 Kaskaden direkt, während übergeordnete Topologien für Schaltsignale und Messungen auf Glasfaserkommunikation zurückgreifen. Das bedeutet, dass eine Skalierbarkeit möglich ist, allerdings nur, wenn Ihr I/O und Ihr Synchronisationsschema von Anfang an entsprechend ausgelegt sind.

Sie sollten auch die Integrationskosten als Teil der Modellkosten berücksichtigen. Zusätzliche FPGA-Kapazität, Signalaufbereitung, Encoder-Schnittstellen und Glasfaserverbindungen lohnen sich, wenn sie das Prototypenrisiko beseitigen oder die Validierung der Steuerung verkürzen. Sie lohnen sich jedoch nicht für jedes Gleichrichter-, Filter- oder Speisemodell. Eine gute Architekturauswahl sorgt dafür, dass hardware an den zeitlichen Bedarf gekoppelt ist und nicht an den vagen Wunsch nach maximaler Genauigkeit in allen Bereichen.

Häufige Modellierungsfehler, die dazu führen, dass CPU-Simulationen Echtzeit-Fristen verpassen

Echtzeit-EMT-Modelle für CPUs scheitern in der Regel an einer kleinen Reihe sich wiederholender Fehler. Die meisten davon entstehen dadurch, dass ein einheitlicher Detaillierungsgrad für Subsysteme erzwungen wird, die sehr unterschiedliche zeitliche Anforderungen haben.

Ein praktischer Überblick über die Harvest -Fall zeigt fünf Fehler auf, die häufig auftreten:

- Zuweisung desselben feinen Zeitschritts sowohl für die schnellen Wandlerzweige als auch für die langsamen Netzwerkabschnitte

- Stark gekoppelte Transformator- und Wandlerblöcke in einem unpartitionierten CPU-Task halten

- Die Modellierung jedes Schaltvorgangs auf der CPU nach der Phasenverschiebung führt zu einer Vervielfachung der Ereignisanzahl

- Die Rückmeldungen von Sensoren und Motoren als sekundär behandeln, selbst wenn der Test im geschlossenen Regelkreis erfolgt

- Erhöhung der Anzahl der Konverterzellen, ohne die Grenzen I/O und Synchronisation neu zu definieren

Ein Team, das ein kaskadiertes Antriebsmodell entwickelt, wird schon früh an diese Grenzen stoßen. Auf Seite 5 wird erläutert, warum eine Ausführung mit mehreren Geschwindigkeiten und Entkopplung wichtig sind, während Seite 2 zeigt, wie schnell die Anzahl der Schaltvorgänge und die Kopplung ansteigen. Verpasste Fristen sind in der Regel kein Zeichen dafür, dass EMT unmöglich ist. Sie sind vielmehr ein Zeichen dafür, dass die Modellarchitektur generisch geblieben ist, obwohl das Schaltproblem nicht mehr generisch war.

„Eine schlechte Aufteilung verursacht mehr Probleme an der Schnittstelle, als sie durch den Solver gelöst werden können; daher sollte die Grenze zwischen CPU und FPGA dem Schaltverhalten folgen und nicht organisatorischen Gewohnheiten.“

Hybridplattformen aus CPU und FPGA bieten Skalierbar für komplexe Tests

Hybridplattformen bieten die beste Lösung für komplexe HIL-Anwendungen, da sie die Rechenmethode an das elektrische Verhalten anpassen. Deshalb setzt sich eine disziplinierte Aufteilung immer wieder gegen den Ehrgeiz einer reinen CPU-Lösung und die Übertreibung einer reinen FPGA-Lösung durch.

Der überzeugendste Beweis ist operativer, nicht theoretischer Natur. Auf den Seiten 5 und 6 wird ein Aufbau gezeigt, bei dem digitale Motor- und Sensormodelle riskante physikalische Tests die Steuerungsüberprüfung, Fehlerprüfungen, Tests mit mehreren Motoren und die Reproduktion von Problemen ersetzt haben. Diese Vorteile stammte die schnell schaltenden Teile dort eingesetzt wurden, wo sie hingehörten, die langsameren Abschnitte kostenbewusst gestaltet wurden und zeitliche Beschränkungen von Anfang an als Designvorgabe berücksichtigt wurden.

Das ist der Maßstab, den Sie für Ihren eigenen Prüfstand anlegen sollten. Eine saubere Hybridausführung verhindert, dass Sie die Plattform überdimensionieren und den Wandler zu stark vereinfachen. OPAL-RT fügt sich nahtlos in diese Schlussfolgerung ein, denn der entscheidende Vorteil liegt nicht hardware der hardware . Der entscheidende Vorteil ist ein Arbeitsablauf, der es Ihnen ermöglicht, schnelle EMT-Schaltungen auf dem FPGA zu platzieren, umfangreichere Anlagenteile auf der CPU zu belassen und wiederholbare HIL-Ergebnisse zu erzielen, ohne auf Vermutungen angewiesen zu sein.

EXata CPS wurde speziell für die Echtzeit-Performance entwickelt, um Studien von Cyberangriffen auf Energiesysteme über die Kommunikationsnetzwerkschicht beliebiger Größe und mit einer beliebigen Anzahl von Geräten für HIL- und PHIL-Simulationen zu ermöglichen. Es handelt sich um ein Toolkit für die diskrete Ereignissimulation, das alle inhärenten physikalischen Eigenschaften berücksichtigt, die sich auf das Verhalten des (drahtgebundenen oder drahtlosen) Netzwerks auswirken werden.