ARTEMiS Inlined Time-stamped Bridge in zweistufigen VSC-basierten HVDC-Anwendungen

Leistungselektronik

2016-10-06

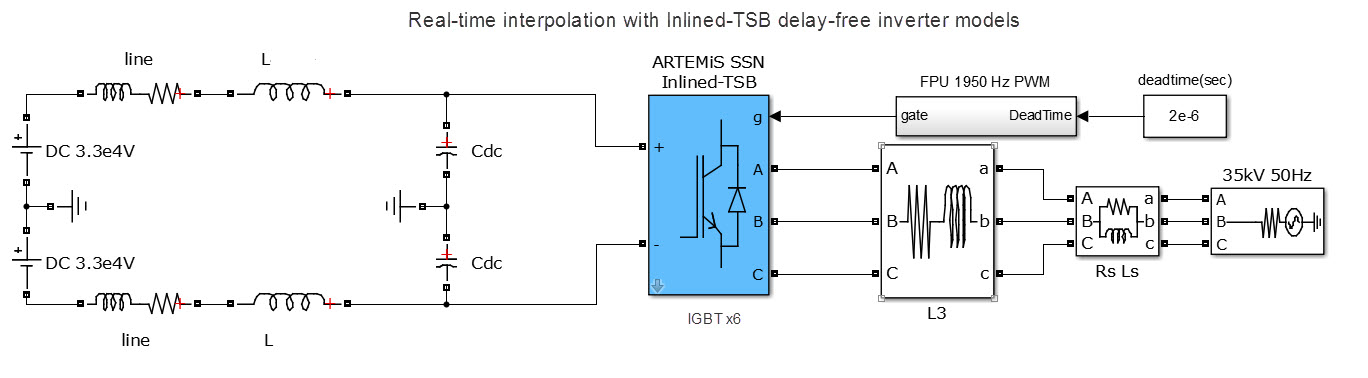

SSN-Simulation von VSC-HVDC mit Inlined Voltage Inverter Compensation (IVIC)

Die Schaltung zeigt, dass ARTEMiS in der Lage ist, 2-Level Voltage Source Converter (VSC)-HVDC-Schaltungen genau zu simulieren

ARTEMiS enthält einen neuartigen Interpolationsalgorithmus für 2-Level-Wechselrichter, der dem Mittelwertbildungs-Wechselrichtermodell mit Interpolation (auch Time-Stamped Bridge -TSB genannt) sehr ähnlich ist.

Der Hauptunterschied zwischen diesem Modell und TSB besteht darin, dass es zwischen dem Wechselrichter und dem Rest der Schaltung KEINE VERZÖGERUNGSVERZÖGERUNG gibt.

In einigen Schaltungen wie VSC-HVDC ist eine verzögerungsfreie Lösung zwingend erforderlich, um eine genaue Simulation mit relativ großen Zeitschritten zu erhalten. Außerdem kompensiert die 'Inlined TSB' nicht nur die Ausgangsspannung, sondern auch den Eingangsstrom der Brücke, ein kritischer Aspekt in dieser Demo.

In dieser Demo beträgt die Abtastzeit 20us, die PWM-Frequenz 1950 Hz und eine Totzeit von 2 us wird auf die PWM-Zündung angewendet.

Die Simulation zeigt, dass die Strom- und Spannungsamplituden einen vernachlässigbaren Jitter aufweisen.