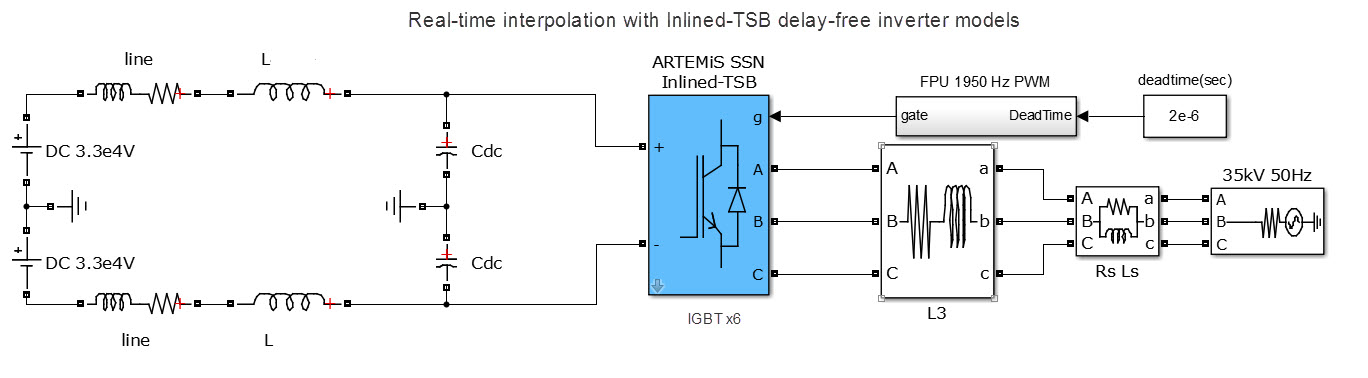

Pont temporel intégré ARTEMiS dans les applications HVDC basées sur des VSC à deux niveaux

Électronique de puissance

2016-10-06

Simulation SSN d'un VSC-HVDC avec compensation de l'onduleur de tension en ligne (IVIC)

Le circuit montre la capacité d'ARTEMiS à simuler avec précision des circuits de convertisseur de source de tension (VSC)-HVDC à 2 niveauxARTEMiS

ARTEMiS intègre un nouvel algorithme d'interpolation pour les onduleurs à 2 niveaux, très similaire au modèle d'onduleur à moyenne avec interpolation (également appelé Time-Stamped Bridge -TSB).

La principale différence entre ce modèle et le TSB est qu'il n'y a PAS de délai de découplage entre l'onduleur et le reste du circuit.

Dans certains circuits comme le VSC-HVDC, une solution sans délai est obligatoire pour obtenir une simulation précise à un pas de temps relativement important. En outre, la BST en ligne compense non seulement la tension de sortie, mais aussi le courant d'entrée du pont, un aspect critique dans cette démonstration.

Dans cette démonstration, l'échantillon est de 20us, la fréquence PWM est de 1950 Hz et un temps mort de 2 us est appliqué au tir PWM.

La simulation montre que les amplitudes du courant et de la tension ont une gigue négligeable.