10 erreurs courantes dans la validation de l'électrification et comment les éviter

Électronique de puissance

01 / 15 / 2026

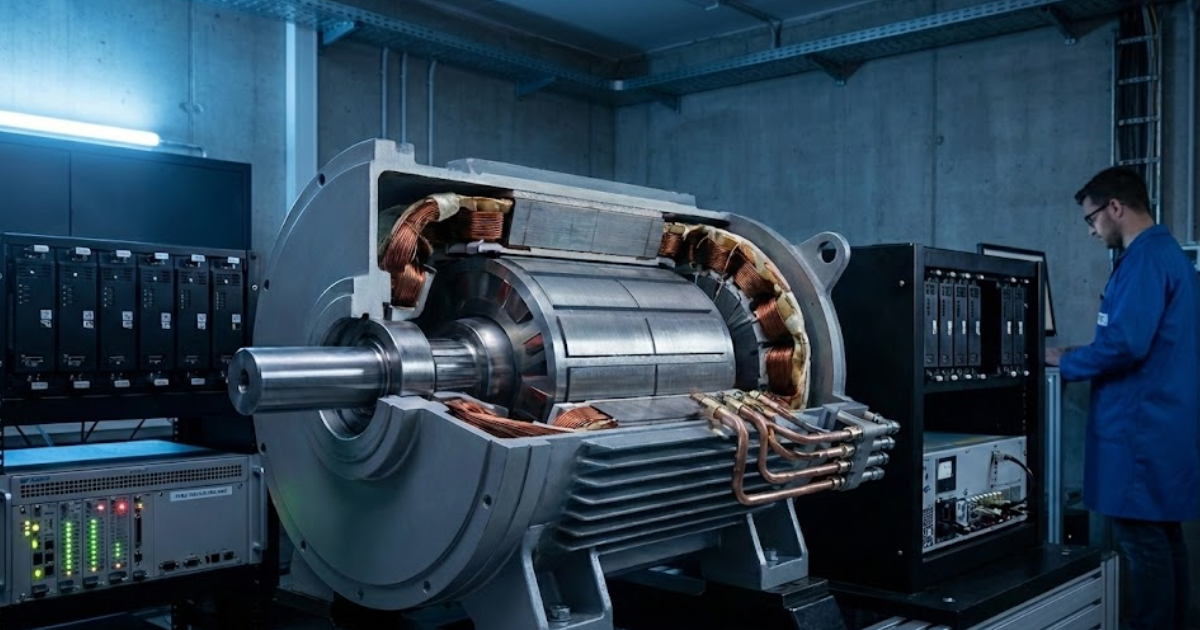

Principaux enseignements

- La marge de synchronisation et la latence d'E/S doivent être considérées comme des exigences de réussite ou d'échec.

- La fidélité de l'installation doit correspondre aux boucles, limites et défauts que vous validerez.

- Les vérifications d'interface et les déclencheurs d'erreur doivent être vérifiés avant d'ajouter de la complexité.

La validation de l'électrification ne sera valable que lorsque les résultats Simulation HIL HIL) correspondront au comportement du matériel. De nombreuses erreurs de validation de l'électrification restent cachées jusqu'à ce que le timing et les E/S se heurtent à des contraintes réelles. Un contrôleur qui semble stable sur un graphique de bureau se mettra à sonner dès que le retard de l'ADC aura une incidence. Détecter rapidement les pièges du HIL permet de gagner des semaines et d'éviter les faux résultats positifs.

Les erreurs de simulation en temps réel proviennent généralement des pas de temps, des interfaces ou des limites manquantes. Un modèle mathématiquement correct échouera toujours à respecter un délai fixe. Un câblage soigné injecte toujours des erreurs d'unité ou de signe via un canal. Traitez le banc HIL comme un instrument de mesure, et chaque incompatibilité deviendra alors exploitable.

« La simulation en temps réel est un système chronométré, pas une rediffusion. »

Pourquoi la validation de l'électrification échoue-t-elle même avec des configurations HIL avancées ?

La validation échoue lorsque les résultats ne se répètent pas avec le même code et le même câblage. Les décalages temporels et les retards cachés créent une fausse stabilité ou de faux défauts. Une réussite ne prouve alors que la configuration de votre banc d'essai, et non votre logique de contrôle. La confiance dans les tests diminue rapidement dès que cet écart apparaît.

Une boucle de vitesse passe hors ligne, puis se déclenche parce que l'échantillon ADC (convertisseur analogique-numérique) arrive une période PWM (modulation de largeur d'impulsion) plus tard que prévu. Ce décalage réduit la marge de phase et transforme une boucle stable en un cycle limite. Traitez le décalage comme une mesure et vérifiez le temps de tâche, la latence d'E/S et la stabilité du solveur avant de régler les gains. Des bases solides rendent les tests de défaillance et les limites thermiques significatifs.

10 erreurs de validation de l'électrification qui compromettent la fiabilité des tests

La plupart des écueils liés au HIL sont dus à un décalage temporel, à des données physiques manquantes ou à des interfaces non vérifiées. Chaque erreur peut faire l'objet d'une vérification rapide que vous pouvez effectuer en laboratoire en moins d'une journée. Une boucle de courant de 20 kHz qui semble stable hors ligne oscillera lorsque les délais ne seront pas respectés. Commencez par la première défaillance que vous pouvez mesurer.

1. Traiter la simulation en temps réel comme une relecture de modèle hors ligne

La simulation en temps réel est un système chronométré, pas une rediffusion. Une installation qui semble fonctionner correctement à 1 ms hors ligne échouera à 50 µs. L'exécution par étapes fixes et le délai d'E/S modifieront la phase de boucle et les niveaux de bruit. Figez rapidement la taille des étapes, modélisez les délais et profilez la marge d'exécution.

2. Accepter le comportement instable du solveur comme une limite de la modélisation

L'instabilité du solveur est un défaut de validation, et non une bizarrerie de modélisation. Une pointe de commutation de diode fera exploser une mise à jour d'état naïve et simulera un défaut de contrôle. Le réglage autour de l'oscillation numérique masque le véritable problème de boucle que vous devez corriger. Choisissez un solveur discret stable, brisez les boucles algébriques et vérifiez les marges de stabilité.

3. Simplification de l'électronique de puissance au-delà de la pertinence de la boucle de contrôle

Les simplifications échouent lorsqu'elles suppriment les dynamiques que vos boucles doivent gérer. Un onduleur idéal masque le temps mort, l'ondulation et la quantification du capteur de courant. Votre régulateur de courant passera hors ligne, puis provoquera un pic sur le matériel. Conservez les délais et les limites de l'onduleur qui correspondent à votre chaîne de détection.

4. Ignorer les effets de couplage électromagnétique dans les machines multiphases

Les machines multiphasées comprennent un couplage qui façonne les défauts et les observateurs. Une machine synchrone à aimant permanent (PMSM) couplée à 12 phases tirera le courant vers les phases saines pendant une ouverture de phase. Un modèle découplé manquera l'ondulation du couple et les courants transversaux. Validez les termes de couplage même lorsque l'installation fonctionne sur un réseau de portes programmables (FPGA) avec OPAL-RT.

5. Test des points de fonctionnement nominaux plutôt que des conditions de défaillance

Les points nominaux masquent les cas qui déclenchent la protection et saturent les boucles. Une chute de 15 % du bus CC déclenchera un effet de bobinage et un pic de courant. Les chemins de défaut exposent les limiteurs, les observateurs et les déclassements thermiques. Effectuez rapidement des injections de défaut et vérifiez l'anti-bobinage et les déclenchements.

6. Désalignement des taux d'échantillonnage de contrôle avec l'exécution matérielle

Le moment d'échantillonnage détermine le retard, et le retard détermine la marge de stabilité. Un échantillon ADC arrivant au milieu de la période PWM déplace la phase effective. Les désynchronisations entraînent des ondulations dans la bande de contrôle et créent de fausses oscillations. Documentez la chaîne de synchronisation, alignez les horloges et mesurez la gigue au niveau des broches.

7. Faire confiance aux modèles de plantes sans vérification de l'interface matérielle

Les interfaces cassent les tests plus rapidement que la physique des installations. Un renversement de signe sur un canal actuel rend la rétroaction positive. Les tracés semblent toujours plausibles alors que les protections se déclenchent et les limites se bloquent. Vérifiez les unités, la mise à l'échelle et le décalage à l'aide de stimuli connus avant de fermer la boucle.

8. Augmenter la complexité des tests sans valider les marges de déterminisme

La complexité vous fait perdre du temps sur votre budget fixe. Une journalisation à haut débit entraînera des dépassements et des fluctuations dans un cas stable. Les fluctuations se traduisent alors par du bruit, des ondulations ou de faux défauts. Conservez une marge, limitez les journaux et déplacez les tâches non critiques hors du cœur en temps réel.

9. Séparation de la validation des commandes des contraintes matérielles liées à l'alimentation électrique

Le code de contrôle s'inscrit dans les limites matérielles, et non dans des calculs mathématiques idéaux. Un comptage de temporisation de la résolution PWM provoquera un bourdonnement. Le temps mort, la quantification et la saturation remodèleront le comportement de la boucle. Modélisez ces limites et testez-les avec le format numérique que vous expédiez.

10. Supposer que l'utilisation d'un FPGA garantit automatiquement la fidélité du modèle

Le timing FPGA masquera les problèmes si l'installation est incorrecte. Une constante de force contre-électromotrice (FCE) décalée de 20 % faussera les estimations de couple. Le déterminisme donnera l'impression que les mauvais paramètres sont stables et reproductibles. Balayez les points de fonctionnement et remontez chaque paramètre jusqu'à sa source.

| Qu'est-ce qui ne va pas ? | Qu'est-ce qui renforcera vos tests ? |

| 1. Traiter la simulation en temps réel comme une relecture de modèle hors ligne | Conception pour une synchronisation à pas fixe et des délais d'E/S mesurés. |

| 2. Accepter le comportement instable du solveur comme une limite de la modélisation | Ne commencez le réglage du contrôle qu'après avoir vérifié la stabilité du solveur. |

| 3. Simplification de l'électronique de puissance au-delà de la pertinence de la boucle de contrôle | Respectez les limites de l'onduleur et les retards que vos boucles rencontreront. |

| 4. Ignorer les effets de couplage électromagnétique dans les machines multiphases | Couplage des modèles afin que les défauts correspondent aux interactions de phase mesurées. |

| 5. Test des points de fonctionnement nominaux plutôt que des conditions de défaillance | Valider les limiteurs et la protection sous contrainte de défaut. |

| 6. Désalignement des taux d'échantillonnage de contrôle avec l'exécution matérielle | Aligner l'échantillonnage et le calendrier des tâches afin que les retards restent prévisibles. |

| 7. Faire confiance aux modèles de plantes sans vérification de l'interface matérielle | Vérifiez le signe, l'échelle et les unités sur chaque canal. |

| 8. Augmenter la complexité des tests sans valider les marges de déterminisme | Conservez une marge temporelle suffisante afin que la journalisation ne crée pas de gigue. |

| 9. Séparation de la validation des commandes des contraintes matérielles liées à l'alimentation électrique | Ajouter PWM et limites numériques afin que le code corresponde à la cible. |

| 10. Supposer que l'utilisation d'un FPGA garantit automatiquement la fidélité du modèle | Valider les paramètres afin que le déterminisme ne masque pas une physique incorrecte. |

Comment hiérarchiser les corrections dans les workflows de modélisation, de matériel et de test

Commencez par la répétabilité, puis ajoutez la fidélité. Vérifiez le budget de pas et le timing des E/S, puis verrouillez la mise à l'échelle et la signature, puis réglez le contrôle, puis exécutez les défauts. L'ordre reste stable pour les entraînements moteurs, les convertisseurs et les systèmes de batterie.

« Se concentrer sur les aspects physiques d'un problème de synchronisation est une perte de temps. »

Une séquence pratique commence par une installation minimale qui exerce toujours le contrôle total, y compris la synchronisation ADC et les points de mise à jour PWM. N'ajoutez de la complexité qu'après avoir réexécuté le même cas avec des formes d'onde correspondantes dans une tolérance stricte. Conservez une liste de contrôle succincte pour chaque nouveau modèle ou cas de test : marge de synchronisation, vérifications d'interface, stabilité du solveur et déclencheurs de défauts. OPAL-RT vous aide à exécuter ce flux de travail en temps réel, mais la rigueur en matière de synchronisation, d'interfaces et de physique permet de gagner la confiance.

EXata CPS a été spécialement conçu pour des performances en temps réel afin de permettre des études de cyberattaques sur les réseaux électriques à travers la couche du réseau de communication de n'importe quelle taille et se connectant à n'importe quel nombre d'équipements pour des simulations HIL et PHIL. Il s'agit d'une boîte à outils de simulation à événements discrets qui prend en compte toutes les propriétés physiques inhérentes qui affecteront le comportement du réseau (câblé ou sans fil).