Des processus de test de micrologiciels plus rapides pour les systèmes embarqués

Simulation

18 mars 2026

Principaux enseignements

- Pour raccourcir les cycles de test du micrologiciel, il faut commencer par mesurer le délai de traitement de bout en bout, puis éliminer le principal goulot d'étranglement avant d'ajouter de nouveaux tests.

- Une pyramide de tests claire permet de garder les vérifications rapides à la portée des développeurs et de réserver les validations nécessitant beaucoup de ressources matérielles aux risques que seuls le timing et les E/S permettent de mettre en évidence.

- Simulation HIL rentable lorsqu'elle fonctionne en mode autonome, avec des réinitialisations stables, des modèles versionnés et des résultats déterministes auxquels on peut se fier.

Toutes les équipes de développement embarqué connaissent bien les désagréments liés aux longues attentes pour obtenir des cartes, des créneaux en laboratoire et des résultats de tests qui arrivent souvent alors que le contexte a déjà changé. Le coût d'un retour d'information trop lent ne se limite pas à la frustration des ingénieurs, car les défauts non détectés se traduisent par des retards dans le calendrier, des retouches et une charge de travail supplémentaire pour le support. On estime qu'une infrastructure de tests logiciels inadéquate coûte à l' 59,5 milliards de dollars par an. L'accélération des tests de micrologiciels est principalement un problème de flux de travail ; la solution commence donc par la manière dont les tests sont organisés, déclenchés et validés.

La voie la plus sûre vers la rapidité consiste à opérer une distinction rigoureuse entre les vérifications rapides qui s'exécutent en continu et les validations plus lentes qui ne s'effectuent que lorsque cela en vaut la peine. Vous raccourcissez les boucles en transférant davantage de défauts vers des vérifications peu coûteuses et reproductibles, tout en concentrant le travail sur le matériel sur ce que seul le matériel peut prouver. Les outils de test de logiciels embarqués ont leur importance, mais le choix de l'outil n'est utile qu'après avoir défini des normes concernant les limites des tests, les résultats déterministes et la responsabilité des défaillances. Les sections ci-dessous se concentrent sur les domaines où le temps est réellement consacré, ce qu'il faut changer en premier lieu et comment déterminer si Simulation HIL dans votre plan de test de micrologiciels.

« La réduction des cycles de test des micrologiciels résulte d'un resserrement des boucles de rétroaction, et non d'une augmentation du nombre de tests. »

Identifiez les étapes les plus chronophages dans les cycles de test des micrologiciels

La plupart des retards dans les tests de micrologiciels sont dus à l'attente, et non à l'exécution des tests elle-même. La saturation des laboratoires, la mise à jour manuelle des micrologiciels, la lenteur du triage et les résultats aléatoires des tests transforment une simple modification de code en une boucle qui s'étire sur plusieurs heures. Lorsque l'on mesure le délai de bout en bout, depuis la validation du code jusqu'à l'obtention d'un résultat fiable (réussite ou échec), le principal goulot d'étranglement apparaît généralement comme une évidence. Il est souvent plus efficace de remédier à cette contrainte unique que d'ajouter de nouveaux tests.

Commencez par suivre trois moments clés pendant une semaine : quand une modification est prête à être testée, quand le test démarre, et quand un développeur en lit le résultat clair. Le délai entre « prêt » et « en cours d'exécution » met en évidence des problèmes de file d'attente, d'accès au matériel ou d'étapes manuelles. Le délai entre « en cours d'exécution » et « compris » met en évidence des journaux de mauvaise qualité, une responsabilité mal définie ou des artefacts manquants, tels que des versions de micrologiciels et des fichiers de configuration. Vous mettrez également en évidence des tâches cachées, comme la réexécution de tests après un redémarrage ou le remplacement de câbles après une réinitialisation du banc d'essai.

Une fois que vous avez identifié ce retard, vous pouvez le traiter comme une contrainte de production. Le matériel de laboratoire partagé nécessite des règles de réservation, automatisation de la réinitialisation et une méthode standard pour rétablir des états de fonctionnement confirmés. Les étapes manuelles doivent s'appuyer sur des scripts et des configurations versionnées, et non sur un savoir tacite. Les instabilités exigent une politique stricte, car un test rapide mais peu fiable ne fera que vous ralentir lors du triage et des discussions.

Mettre en place une pyramide de tests pour les logiciels embarqués et les micrologiciels

Une pyramide de tests pratique pour le développement embarqué concentre la plupart des vérifications là où le retour d'information est le plus rapide et le moins coûteux, puis réserve les validations nécessitant beaucoup de matériel aux risques qui comptent vraiment. Les tests unitaires du micrologiciel et les vérifications des composants doivent être exécutés fréquemment et s'achever rapidement. Les tests d'intégration doivent valider les limites des modules, les hypothèses de synchronisation et la gestion des erreurs. Les tests complets du système embarqué sur le matériel doivent vérifier les E/S, le comportement électrique et le contrôle en boucle fermée, car ce sont ces éléments qui représentent les coûts les plus élevés.

Une bonne façon de définir la pyramide consiste à noter ce que chaque couche doit prouver et ce qu’elle ne doit en aucun cas tenter de prouver. Les tests de bas niveau doivent valider la logique pure, les machines à états et les contrôles de sécurité sans avoir recours à des capteurs ou à des actionneurs. Les tests de niveau intermédiaire doivent valider les interactions avec le pilote, le comportement de planification et la structure des protocoles à l'aide de stubs contrôlés ou de modèles de simulation. Les tests de haut niveau doivent se concentrer sur les cas de sécurité de bout en bout, les réponses aux défaillances et les performances dans des délais réalistes, car ce sont ces éléments qui échouent silencieusement jusqu'à ce que le matériel soit impliqué.

Le compromis réside entre la couverture et la fiabilité. Anticiper les vérifications permet toujours de réduire le coût par exécution, mais seulement si l'on veille sur les interfaces afin que les tests précoces ne s'éloignent pas du produit. Cela implique une séparation claire entre les couches d'accès au matériel et la logique métier, ainsi qu'un contrat versionné définissant les formats de données et la synchronisation. Lorsque la pyramide est clairement définie, on peut dire « non » aux tests lents à la base et « oui » à des tests moins nombreux mais plus précis au sommet.

Automatisez la compilation, la gravure et les tests pour raccourcir les cycles de rétroaction

automatisation réduit les cycles de test du micrologiciel lorsqu'elle élimine l'attente humaine et produit des résultats reproductibles, et non pas simplement lorsqu'elle exécute davantage d'étapes. Un bon pipeline compile, packe, flashe, exécute des tests ciblés et capture les journaux en une seule opération, d'une simple pression sur un bouton. Les meilleurs pipelines enregistrent également le micrologiciel, la configuration et les ressources de test exacts qui ont provoqué une défaillance. Cette traçabilité transforme le triage, qui passe d'une réunion à une correction.

Les gains les plus rapides proviennent généralement de la standardisation des procédures de préparation et de réinitialisation des appareils. Une carte doit pouvoir être programmée et remise en état sans connaissances particulières, même après l'échec d'un test ou le déclenchement du chien de garde. Les journaux de test doivent être lisibles par machine et inclure l'identifiant du micrologiciel, les indicateurs de fonctionnalités et la configuration des E/S afin de pouvoir reproduire les défaillances. Lorsqu'une défaillance survient, la première réaction doit être une réexécution automatisée avec les mêmes éléments, et non une tentative de recréation manuelle.

- Une commande qui compile et empaquette l'image exacte du micrologiciel pouvant être testée

- Mise à jour automatique avec étape de vérification de la lecture ou de la somme de contrôle

- Commande de réinitialisation matérielle qui ramène l'appareil à un état connu

- Enregistrement des journaux qui stocke les artefacts et les données de chronométrage pour chaque exécution de test

- Des règles de réussite/échec claires qui considèrent les tests instables comme des défauts

automatisation impose automatisation une discipline salutaire. Si un test ne peut pas s'exécuter sans surveillance, c'est souvent qu'il dépend trop du jugement d'une personne, d'une particularité du banc d'essai ou d'un cheminement de câbles non documenté. En remédiant à cela, vous réduirez les fausses alertes et faciliterez la mise à l'échelle de votre programme de tests de logiciels embarqués entre les équipes et les sites.

Choisissez des outils de test de logiciels embarqués qui s'intègrent à l'intégration continue (CI)

La rapidité des outils de test de logiciels embarqués dépend entièrement de leurs points d'intégration. Une chaîne d'outils adaptée s'intègre à votre système d'intégration continue (CI), utilise les mêmes artefacts de build que ceux que vous déployez et exporte les résultats dans des formats compatibles avec vos tableaux de bord et vos contrôles qualité. Les outils qui nécessitent une configuration manuelle, des workflows exclusivement basés sur une interface graphique ou des licences ponctuelles entraîneront des délais d'attente, même si l'exécution des tests est rapide. Le choix doit se concentrer sur la reproductibilité, automatisation et les échecs pouvant faire l'objet d'un débogage.

Évaluez les outils à l'aune de trois questions pratiques. Premièrement, peuvent-ils fonctionner en mode sans interface graphique et de manière autonome sur vos agents de compilation, y compris l'accès aux débogueurs, au matériel Flash et aux autorisations requises ? Deuxièmement, peuvent-ils stocker les artefacts et les métadonnées afin qu'une exécution ayant échoué puisse être reproduite à la demande, même plusieurs semaines plus tard ? Troisièmement, peuvent-ils isoler les tests afin qu'un plantage ne compromette pas l'ensemble de la session, ce qui est un problème courant dans les tests de micrologiciels lorsqu'un seul défaut bloque le matériel ?

Les compromis apparaîtront rapidement. Les outils offrant une analyse approfondie du matériel nécessitent souvent une configuration plus complexe, tandis que les frameworks légers peuvent passer à côté de problèmes de synchronisation, d'ordre des interruptions et de cas limites liés aux périphériques. Considérez cela comme un choix technique, et non comme un choix d'achat. Un ensemble réduit d'outils que votre équipe peut automatiser et auxquels elle peut faire confiance sera plus efficace qu'un ensemble volumineux que seuls des experts sont capables d'utiliser.

Utiliser Simulation HIL la validation en boucle fermée

Simulation HIL améliore la validation du micrologiciel, car elle permet de tester votre code de contrôle dans des conditions de synchronisation et de comportement d'E/S réalistes sans attendre la version finale du produit. Une Simulation HIL exécute le micrologiciel du contrôleur sur son matériel cible tandis qu'un simulateur en temps réel fournit les capteurs, les charges et la dynamique de l'installation. Ces tests en boucle fermée permettent de détecter des problèmes que la simulation pure et les vérifications statiques ne permettent pas de repérer, tels que la saturation, la gigue de synchronisation et la gestion des défauts en situation de contrainte. Elle rend également les tests de régression reproductibles une fois que le banc d'essai est stable.

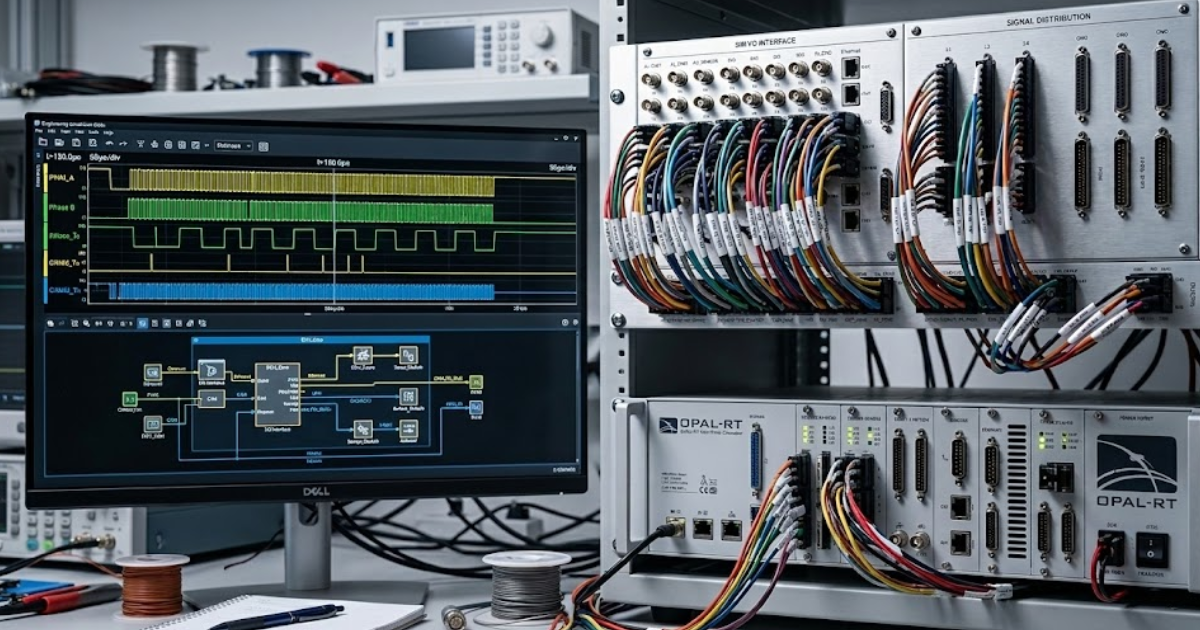

Un scénario concret illustre pourquoi cela est important. Une équipe chargée de tester le micrologiciel de commande d'un onduleur peut faire fonctionner le contrôleur sur son microcontrôleur de production tandis que le simulateur génère des courants de phase, une ondulation du bus CC et des pertes de signal des capteurs, puis vérifier que le micrologiciel passe en mode de sécurité dans un délai strictement défini. Ce même test peut injecter un défaut de blocage sur une entrée et vérifier le chemin de diagnostic, sans risquer d'endommager le matériel ni d'attendre la mise au point d'un étage de puissance complet. Une plateforme qu'OPAL-RT est souvent utilisée pour ce type de validation en boucle fermée lorsque vous avez besoin d'un timing déterministe et d'une injection de défauts reproductible.

Le HIL ne remplace pas les essais au banc, et il vous ralentira s'il se transforme en un projet scientifique fragile. Le banc d'essai nécessite des procédures de réinitialisation stables, des modèles versionnés et une attribution claire des responsabilités tant pour le micrologiciel que pour les ressources de simulation. Commencez par un ensemble restreint de comportements à haut risque dont les avantages sont évidents, puis ne l'élargissez qu'une fois que la première série de tests s'est déroulée sans surveillance. Lorsque la boucle HIL est fiable, elle devient une voie rapide pour les modifications qui, autrement, devraient attendre leur tour pour accéder à un matériel limité.

« L'objectif est d'obtenir un signal fiable, et non une activité maximale. »

Trouver le juste équilibre entre la fidélité de la simulation, le coût et la couverture à toutes les étapes des essais

La rapidité réside dans l'adaptation du niveau de fidélité des tests au risque que vous cherchez à éliminer. Les simulations à haute fidélité et les tests HIL (Hardware-in-the-Loop) offrent une plus grande fiabilité, mais leur mise en place, leur exécution et leur maintenance sont plus coûteuses. Les vérifications à faible fidélité s'effectuent plus rapidement et à un stade plus précoce, mais elles ne prennent pas en compte les effets temporels et physiques. Un processus de travail équilibré attribue à chaque étape un objectif clair, ce qui vous permet d'obtenir une couverture étendue sans transformer chaque modification en un test complet du système.

| Où effectuer le test | Ce qu'il attrape le mieux | Combien cela vous coûte | Quand il fait ses preuves |

| Poste de travail de développeur avec tests unitaires isolés | Erreurs logiques, conditions aux limites et régression dans les algorithmes de base | Configuration simple, mais couverture limitée en termes de synchronisation et d'E/S | Toute modification touchant à la logique métier ou aux machines à états |

| Exécution d'une intégration continue (CI) utilisant des tests de composants avec des stubs | Problèmes d'interface, problèmes de structuration du protocole et voies de gestion des erreurs | Entretien modéré des tiges et des fixations | Lorsque des modules interagissent et que les défaillances doivent être reproductibles |

| test SIL | Maîtriser les tendances en matière de stabilité, les problèmes de séquencement et les hypothèses relatives au calendrier d'intégration | Maintenance des modèles et risque de dérive des modèles lié au matériel | Avant que le matériel ne soit prêt et après d'importantes refontes |

| Essais Simulation HIL | Incidences de la gigue de synchronisation, réactions aux défaillances et cas limites d'E/S en charge | Travaux de montage de l'installation et travaux d'étalonnage en cours | Pour les chemins critiques en matière de sécurité et les défaillances d'intégration dont le débogage est coûteux |

| Essais au banc sur des ensembles matériels complets | Comportement électrique, problèmes d'intégrité du signal et intégration avec les périphériques de production | Temps de laboratoire prolongé, risque accru d'usure du matériel et de variations dans la configuration | Versions candidates et modifications touchant aux interfaces matérielles |

Le coût ne se limite pas à l'aspect financier. Il se traduit également par la maintenance des modèles, les difficultés liées à la planification des laboratoires et la charge cognitive liée au débogage. Le NIST a estimé qu'une meilleure infrastructure de test pourrait réduire l'impact économique des tests inadéquats d'environ 22,2 milliards de dollars, et le message à retenir pour les équipes embarquées est simple : investissez dans les étapes qui éliminent le plus de réexécutions et réduisent au maximum les files d'attente dans les laboratoires. Lorsque chaque étape a une fonction et un point d'arrêt, la simulation et le matériel se complètent au lieu de se faire concurrence pour attirer l'attention.

Évitez les pièges courants liés aux tests des systèmes embarqués qui ralentissent les équipes

Les écueils les plus préjudiciables lors des tests de systèmes embarqués peuvent être évités : des tests instables, une responsabilité mal définie et des configurations matérielles impossibles à rétablir rapidement. La rapidité repose sur la confiance, car tout résultat suspect entraîne de nouvelles exécutions et des réunions. Une suite de tests qui échoue de manière imprévisible ralentira davantage les livraisons qu’une suite plus petite mais déterministe. L’objectif est d’obtenir un signal fiable, et non une activité maximale.

Il faut une politique stricte face à l'instabilité. Si un test échoue et que la première réaction de l'équipe est de le relancer « juste pour voir », la boucle de rétroaction est déjà rompue, et vous en paierez le prix à maintes reprises. La responsabilité est tout aussi importante, car un échec sans responsable clairement identifié se transforme en file d'attente, et c'est dans ces files d'attente que les tests de micrologiciels vont mourir. Le matériel nécessite également la même rigueur que les logiciels, avec un câblage documenté, un contrôle de réinitialisation et un mappage E/S cohérent afin que les résultats aient toujours la même signification.

La rapidité à long terme découle du fait de considérer les tests comme un produit à part entière, avec ses utilisateurs, sa disponibilité et son support, et non comme une tâche secondaire. Lorsque vous investissez dans des bancs d'essai reproductibles, des modèles versionnés et une capture claire des artefacts, chaque correction réduit le coût de la modification suivante. Les équipes qui travaillent avec OPAL-RT constatent souvent cette évolution lorsque les ressources HIL passent d'un travail ponctuel en laboratoire à une capacité maintenue avec des normes claires, car le banc d'essai cesse d'être un goulot d'étranglement et devient une étape fiable. Cette discipline permettra de maintenir des boucles de rétroaction courtes même lorsque la complexité augmente.

EXata CPS a été spécialement conçu pour des performances en temps réel afin de permettre des études de cyberattaques sur les réseaux électriques à travers la couche du réseau de communication de n'importe quelle taille et se connectant à n'importe quel nombre d'équipements pour des simulations HIL et PHIL. Il s'agit d'une boîte à outils de simulation à événements discrets qui prend en compte toutes les propriétés physiques inhérentes qui affecteront le comportement du réseau (câblé ou sans fil).