核心要点

- 时序裕量和I/O延迟应作为合格/不合格要求处理。

- 设备保真度应与您将验证的回路、限值和故障相匹配。

- 在增加复杂性之前,应先验证接口检查和故障触发机制。

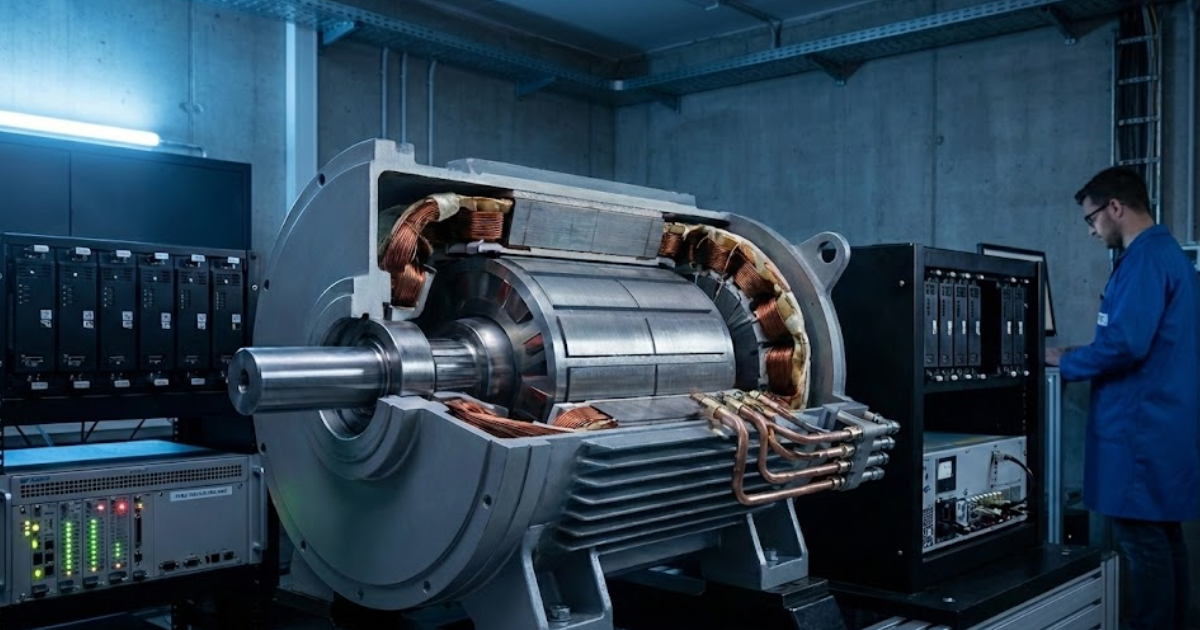

电气化验证仅在硬件在环(HIL)结果与实际硬件行为一致时才有效。许多电气化验证错误在时序和I/O遭遇真实限制前始终隐匿。即便在桌面图表中看似稳定的控制器,一旦ADC延迟成为关键因素便会出现振荡。及早发现HIL陷阱可节省数周时间,并避免错误通过验证的结果。

仿真错误通常源于时间步长、接口或缺失的限制条件。即使数学上正确的模型,在固定步长时限下仍会失败。即使布线规范,单一通道仍可能引入单位或符号错误。将硬件在环测试台视为测量仪器,如此每处偏差都可转化为可执行的改进措施。

仿真 定时系统,而非回放。

为何即使采用先进的硬件在环(HIL)系统,电气化验证仍会失败

当相同代码和接线条件下测试结果无法复现时,验证即告失败。时序偏差与隐性延迟将导致虚假稳定性或虚假故障。此时通过的测试仅验证了台架设置,而非控制逻辑。一旦出现这种偏差,测试可信度将急剧下降。

速度环路脱离在线状态后跳闸,原因是ADC(模数转换器)采样比预期延迟一个PWM(脉宽调制)周期。该延迟位移削减了相位裕度,使稳定环路转为极限环。将失配视为测量误差,在调整增益前需验证任务时间、I/O延迟及求解器稳定性。扎实的基础设计使故障测试和热极限测试具有实际意义。

10个损害测试可信度的电气化验证错误

大多数硬件在环(HIL)测试的陷阱可追溯至时序错配、物理特性缺失或接口未验证。每种错误都可通过台式设备在一天内快速检测。看似稳定的20kHz电流回路,一旦时限延误便会产生振荡。请从首个可量化的故障点着手排查。

1. 将实时仿真 离线模型回放

实时仿真 定时系统,而非回放。在1毫秒离线状态下看似正常的被控对象,在50微秒时会发生故障。固定步长执行与I/O延迟将改变回路相位和噪声底限。需提前冻结步长大小、建模延迟,并分析执行余量。

2. 将求解器的不稳定行为视为建模限制

求解器不稳定性是验证缺陷,而非建模怪癖。二极管换向尖峰会破坏简单的状态更新,并伪造控制故障。围绕数值振铃进行调试会掩盖必须解决的真实回路问题。请选择稳定的离散求解器,打破代数回路,并验证稳定性裕度。

3. 超越控制回路相关性,简化电力电子技术

简化设计会因忽略回路必须处理的动态特性而失效。理想逆变器应隐藏死区时间、纹波及电流传感器的量化误差。当前稳压器会脱离在线状态,继而在硬件端产生电流尖峰。请确保逆变器延迟与限制参数与您的传感链相匹配。

4. 多相电机中电磁耦合效应的忽略

多相机器包含塑造故障与观测器的耦合机制。当某相断开时,耦合的12相永磁同步电机(PMSM)会将电流引入正常相。解耦模型则会遗漏转矩纹波与交叉电流。即使在基于FPGA的系统上运行,仍需通过OPAL-RT验证耦合项。

5. 测试额定工作点而非故障工况

标称点隐藏了触发保护和饱和回路的情况。15%的直流母线电压下陷将引发饱和效应和电流尖峰。故障路径暴露了限流器、观测器和热降额。需尽早进行故障注入测试,并验证反饱和保护和跳闸功能。

6. 控制采样率与硬件执行时序错位

采样时序决定延迟,延迟决定稳定裕度。若ADC采样落在PWM周期中点,将导致有效相位偏移。速率不匹配会将纹波混叠至控制带宽,引发虚假振荡。需记录时序链、对齐时钟,并在引脚处测量抖动。

7. 在未进行硬件接口验证的情况下信任植物模型

接口故障比设备物理故障更快导致测试失败。电流通道上的指示翻转会使反馈转为正向。当保护装置跳闸且限值被钳位时,曲线图仍看似合理。闭环前务必使用已知刺激信号验证单元、量程及偏移量。

8. 在未验证确定性余量的情况下扩展测试复杂度

复杂性会侵蚀固定步长预算中的时间。高频率日志记录会将稳定场景推向超时和抖动。抖动进而表现为噪声、纹波或虚假故障。请保持余量、限制日志记录,并将非关键任务移出实时核心。

9. 将控制验证与功率硬件约束分离

控制代码受限于硬件边界,而非理想数学模型。单次定时器计数产生的PWM分辨率将引发占空比抖动。死区时间、量化误差与饱和效应将重塑控制回路行为。请对这些限制进行建模,并使用形式 数值形式 进行测试。

10. 假设使用FPGA就能自动保证模型保真度

若系统模型错误,FPGA时序会掩盖问题。反电动势常数偏差20%将导致扭矩估算偏差。确定性特性会使不良参数看似稳定可重复。需扫描工作点并将每个参数追溯至源头。

| 出了什么问题 | 什么能使你的测试更严谨 |

| 1. 将实时仿真 离线模型回放 | 设计用于固定步进时序和测量I/O延迟。 |

| 2. 将求解器的不稳定行为视为建模限制 | 仅在求解器稳定性检查通过后才开始控制调谐。 |

| 3. 超越控制回路相关性,简化电力电子技术 | 保持逆变器限制,并延迟您的回路将看到的情况。 |

| 4. 多相电机中电磁耦合效应的忽略 | 模型耦合使故障与测得的相间相互作用相匹配。 |

| 5. 测试额定工作点而非故障工况 | 验证故障应力下的限流器和保护装置。 |

| 6. 控制采样率与硬件执行时序错位 | 协调采样与任务时序,确保延迟可预测。 |

| 7. 在未进行硬件接口验证的情况下信任植物模型 | 确认每个通道的标记、缩放比例和单位。 |

| 8. 在未验证确定性余量的情况下扩展测试复杂度 | 保持时序余量,以确保日志记录不会产生抖动。 |

| 9. 将控制验证与功率硬件约束分离 | 添加PWM和数值限制,使代码与目标相匹配。 |

| 10. 假设使用FPGA就能自动保证模型保真度 | 验证参数,确保确定性不会掩盖错误的物理模型。 |

如何在建模、硬件和测试工作流中优先处理修复方案

从可重复性开始,再增加保真度。验证步进预算和I/O时序,然后锁定缩放和符号,接着调整控制,最后运行故障测试。该顺序在电机驱动器、换流器系统中保持稳定。

在时序问题之上强行修复物理逻辑是徒劳的。

实用流程应从最小化系统开始,该系统仍需完整执行控制路径,包括ADC时序和PWM更新点。仅当相同测试案例在严格公差范围内重现匹配波形时,才增加复杂度。针对每个新模型或测试案例,需保持简短检查清单:时序裕度、接口验证、求解器稳定性及故障触发点。OPAL-RT可实时执行该工作流,但唯有在时序、接口和物理特性方面保持严谨,方能赢得信任。

EXata CPS 专为实时性能而设计,可通过任何规模的通信网络层和连接任何数量的设备进行 HIL 和 PHIL 仿真,从而对电力系统的网络攻击进行研究。这是一个离散事件仿真 工具包,考虑了所有会影响网络(有线或无线)行为的固有物理属性。