核心要点

- 当您验证完整的闭环系统而非孤立部件,并将时序和保护措施作为需量化的要求时,您的产品出货可靠性将显著提升。

- 通过/失败标准能为您节省数周时间,因为它将调试争论转化为明确的操作,这些操作与阈值相关联,可在不同固件版本中重复执行。

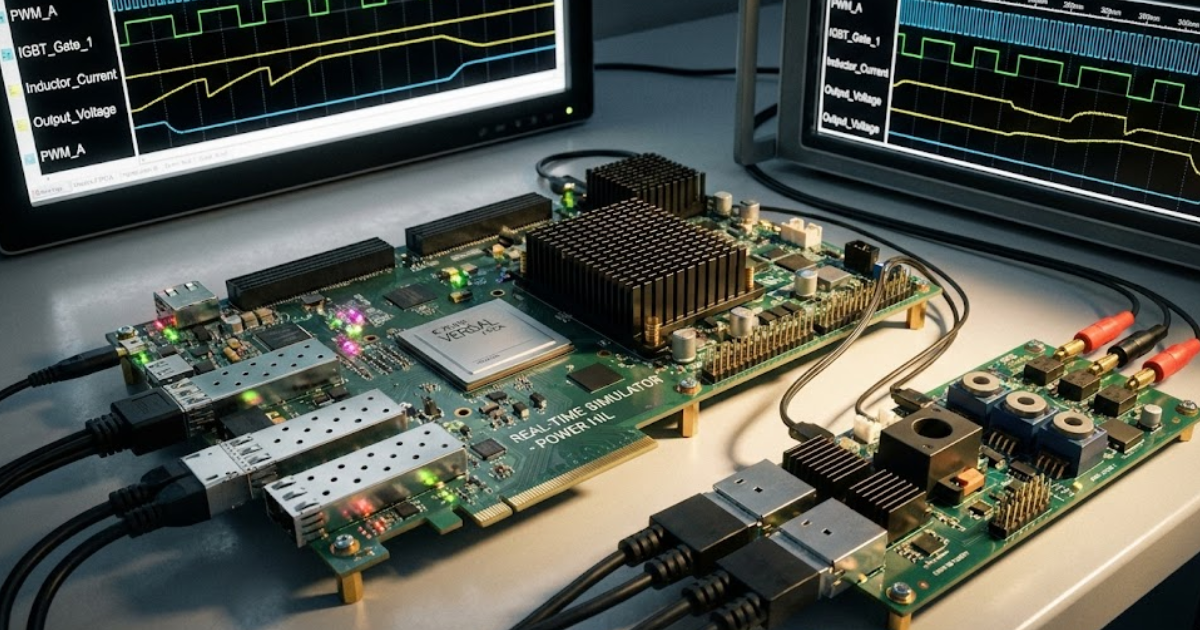

- 实时仿真 硬件在环测试适用于时序、I/O和故障序列决定结果的场景,而不仅限于模型表现稳定的场合。

电气化验证可确保控制代码和电源硬件在首次全功率运行时不会出现意外。电动汽车销量接近1500万辆,约占 占汽车总销量的18%,因此更多高压系统正面临紧迫的交付周期。后期故障往往始于时序与保护机制的异常,最终演变为返工问题。

可靠的程序将时序、功率流和控制视为一个耦合系统。离线模型有助于设计,但实时仿真 HIL测试会揭示由固定步长、I/O延迟和噪声信号导致的缺陷。

电气化验证在组件级测试计划之外还需哪些内容

电气化验证的有效性取决于能否在与固件相同的工作边界下验证完整的闭环系统。控制器时序、传感器路径、执行器极限及保护机制均需作为整体系统进行测试。仅检查单个组件将导致接口故障无法被发现。 集成后常见疏漏:逆变器与电机各自通过测试,组合回路却在扭矩阶跃时跳闸。电流偏移、PWM时序或解析器解码异常都可能将控制器推入边界情况。 将集成测试视为首要任务。增加延迟预算和模式转换测试。注入预期故障,如传感器失效或直流母线电压下陷。

“通过/失败标准可防止验证演变为无休止的调试。”

如何为电气化系统定义合格/不合格判定标准

通过/失败标准可防止验证演变为无休止的调试。每个标准都需要测试条件、观测信号以及触发动作的阈值。除稳态目标外,还需纳入时序和保护结果。 仅设定扭矩目标会掩盖故障模式。需同时设定峰值电流、恢复时间及保护反应时间的限制。这些细节决定了当设备异常运行时系统能否保持安全。

使用可在每次固件更新中重复的标准:

- 峰值电流在负载阶跃期间始终低于限值。

- 保护将在短暂事件发生后于时限内作出反应。

- 直流母线纹波在关键点保持在限值范围内。

- 扭矩误差在整个周期内保持在容差带内。

- 故障恢复在时限内达到安全状态。

如何选择实时仿真 离仿真

仿真 仿真 主要区别仿真 墙钟时间约束。离线运行忽略时间因素,因此可进行参数扫描和长时间案例运行;实时运行则强制执行固定步长,从而能够验证调度机制、I/O延迟及保护序列。

离线模式最适合处理设计问题,例如增益调整。实时模式最适合处理实现问题,例如采样顺序和时限余量。将实时模式用作对固件行为的验证手段。

| 您需要解答的验证问题 | 离线仿仿真 | 实时仿真 |

| 在整个操作图谱中的稳定性 | 你需要快速浏览所有案例。 | 必须锁定步长和采样顺序。 |

| 时序与通信限制 | 你可以假设理想延迟。 | 必须包含总负载和延迟。 |

| 故障下的保护反应时间 | 你想要长瞬态。 | 你需要在严格的时间控制下进行精确的顺序操作。 |

| 开关纹波影响检测 | 你可以容忍墙面时间较慢。 | 你需要确定性的小步推进。 |

| 非理想输入/输出下的集成环路行为 | 您正在塑造建筑。 | 您正在验证循环步频。 |

硬件在环测试在电气化验证工作流中的定位

硬件在回路(HIL)测试适用于控制器硬件必须与实时响应的实际设备协同运行的场景。它弥合了仿真 与首次高压台架测试之间的差距,同时避免在脆弱的原型机上进行高风险故障测试。 典型配置中,电机控制ECU将与模拟逆变器、机械设备及负载协同运行。您无需启动实体硬件即可测试校准、通信时序及故障处理能力。通过可重复的轨迹记录,中断遗漏与缩放误差将迅速显现。

从验证循环时序的最小化系统开始。实现回归测试自动化,确保每次固件更新都能重现相同的运行周期和故障。将硬件在环测试结果作为版本发布的验证依据。

如何在时序和I/O限制下验证控制软件

若在实验室中将时序精度视为"足够接近",控制软件必将失效。控制器运行于带时限的调度器中,需应对共享总线与中断突发。验证必须证明:控制回路满足速率要求,采样保持一致性,保护机制在负载下仍能执行。 常见模式是离线状态下曲线稳定,硬件运行时却出现噪声。高通信负载会推迟电流环路响应,相位延迟则侵蚀稳定裕度。另一种模式是计算峰值期间传感器出现毛刺,导致回退动作延迟。

将任务耗时和逾期视为合格/不合格信号。强调消息负载并注入抖动。包含真实的ADC量化与滤波延迟。

如何在不损坏硬件的情况下测试电力电子器件的行为

在进行全功率运行前验证保护措施和序列控制,可提升电力电子测试安全性。开关故障可能损毁原型机,因此需先在受控回路中验证跳闸逻辑和栅极控制顺序。硬件测试应验证行为而非发现问题。 预充电程序可能因估算器假设直流母线缓慢上升而跳闸。某一温度下设定的死区时间可能导致另一温度下发生交叉传导。当限值响应延迟时,负载突降期间可能出现过电压尖峰。

首先采用平均化逆变器模型验证极限值与控制结构。仅当开关细节改变您判断的信号时,才需转向该细节。注入明确故障并记录反应序列。

如何在故障条件下验证电动机控制

机器控制验证必须涵盖故障情况,因为不安全行为首先在此显现。您需要证明当相位缺失或传感器漂移时,扭矩限制、电流限制和热保护仍能保持稳定。目标是实现受控降级,并快速响应至安全状态。 电动汽车案例:高扭矩启动时发生开相故障。执行器案例:位置步进过程中解析器失效。控制器必须检测故障、重构参考值,并确保电压电流维持在限值范围内。

注入与拓扑结构匹配的故障,而非通用标志。验证检测时间和回退行为。确保各模式下限制值保持一致,以维持校准的合理性。

选择能够保持稳定、实现自动化并支持审计的堆栈。

多相机器在测试范围和工具方面发生了哪些变化

多相电机因其容错特性产生多种有效运行模式,从而扩展了测试范围。增加相数可平滑转矩并降低单相电流,但需增设传感器、门控模式及重构逻辑。验证工作必须涵盖模式转换、故障隔离及各相组限值。 当12相永磁同步电机(PMSM)的相组间存在电磁耦合时,故障处理将更具复杂性。单相缺失会重塑多通道间的电流分配与磁通耦合关系。系统重构必须在满足热限制的前提下处理这些变化。

按模式和故障类型分别维护测试向量。为每种模式设定专属的通过/失败判定标准,确保证据清晰可辨。将每种模式转换视为独立测试,而非附注。

FPGA实时仿真 如何仿真 快速切换保真度

当保护措施依赖于微秒级时序时,FPGA实时仿真 。FPGA执行可实现更小的时间步长与确定性时序,从而确保门市场活动 采样时刻保持同步。在高开关频率下,仅靠CPU循环难以维持这种同步性。 饱和度检测与电流重建是常见痛点。这些功能在离线状态下看似正常,但精确计时环境下却可能失效。部分团队采用OPAL-RT基于FPGA的仿真 在闭环测试中仿真 这些关联关系的稳定性。

将切换关键模块放置于FPGA上,其余低动态模块保留在其他位置。参照安全、限功配置进行关联验证后,冻结模型版本。此举可确保时序证据的可重复性。

常见的电气化验证失败案例,这些失败往往导致时间和预算的浪费

当团队将模型成功误认为系统就绪时,就会浪费时间。紧密耦合会将缺陷推向接口,导致延迟与限制相互作用。团队还常跳过故障注入环节,最终在硬件层面首次遭遇故障。 现场问题的规模揭示了严苛审查的严峻性。2023年间,1000起召回事件覆盖 超过3900万辆 的车辆及设备。当质疑来临时,验证证据必须经得起考验。

保护逻辑被单独处理时,就会与控制器产生冲突。时序被视为"足够接近"时,抖动问题便会浮现。若将集成测试、时序测试和故障测试提前进行,这些问题便会不攻自破。

如何为您的程序选择合适的验证堆栈

选择验证方案本质上是对容忍失效阈值的判断。高安全风险需尽早采用实时仿真和硬件在仿真。概念验证阶段则应增加离线扫描,减少硬件循环。 从最高风险交互环节着手。时序风险指向需模拟真实I/O与调度器压力的HIL测试;切换风险则需在驱动波纹与保护机制的部件上采用小时间步长。

执行纪律比任何单一工具的选择更为重要。当您需要确定性实时行为和固件更新间可重复验证时,OPAL-RT正是理想之选。请选择能够保持稳定、实现自动化并支持审计的软件栈。

EXata CPS 专为实时性能而设计,可通过任何规模的通信网络层和连接任何数量的设备进行 HIL 和 PHIL 仿真,从而对电力系统的网络攻击进行研究。这是一个离散事件仿真 工具包,考虑了所有会影响网络(有线或无线)行为的固有物理属性。