核心要点

- 在CPU与FPGA的选择中,应以固定时间步长、最坏情况延迟和抖动限制为起点,因为错过时限将比任何建模妥协更快速地使硬件在环测试结果失效。

- 在需要快速迭代、大型多域模型和频繁更新时使用CPU,而在开关、保护和I/O时序必须在每个采样点保持确定性时则采用FPGA。

- 通过严格的任务划分实现最佳成本与进度效果:仅将时间关键路径保留在FPGA上,其余部分交由CPU处理,使团队能够无障碍地调试和更新模型。

当模型需要灵活性时选择CPU,当模型需要确定性亚微秒级定时时选择FPGA。

该选择至关重要,因为实时电力电子仿真 很少仅仿真 数学限制;它受限于时间步长、I/O时序以及保留的开关细节程度。电力电子系统已处理约 70%的电力 ,这正是验证压力同时作用于功率级、控制系统、保护装置及电网交互的原因。若仿真器未能满足时限要求,控制器测试便沦为时序测试而非控制性能验证。

基于CPU的仿真 覆盖大量硬件在环(HIL)工作,因其具备快速构建、迭代和调试的优势。当开关、传感或保护路径必须在每个采样点都像硬件那样运行,且对延迟和抖动有严格限制时,基于FPGA的仿真 其价值。将此视为划分与计时问题而非处理器竞争的团队,能更快获得稳定结果。

将求解器时间步长目标匹配至CPU或FPGA

当固定时间步长可维持在数十微秒且仍能满足测试目标时,CPU是最佳选择。当固定时间步长必须降至个位数微秒或更低且仍需满足所有时限要求时,FPGA才是理想方案。首要考量并非精度,而是调度能力——若仿真器无法按时完成每个步骤,其结果便不再可信。

从必须实时闭合的最快回路开始,然后向外推进。栅极驱动和保护逻辑迫使你采用最小时间步长,而热管理或能源管理模型则容忍较大的步长。CPU求解器擅长处理大量连续状态,当需要每日切换模型变体、实时调整参数或跨核心进行批量扫描时,它们尤为出色。当并行执行和固定延迟比浮点运算的便利性更重要时,FPGA求解器便大放异彩。

时间步长的选择同样决定了系统在不产生数值伪影前提下可呈现的精度。若步长设置过小,导致尖锐的边界信号在相邻采样点间产生模糊,将导致电流纹波与峰值数据失真。若目标是实现控制器稳定性与平均功率流,采用较大步长及平均化模型是合理选择;若需实现周期性保护时序或电流限制,则时间步长将直接决定CPU运算能力的硬性下限。

比较延迟、抖动和I/O时序要求

CPU与FPGA时序的主要区别在于确定性。

CPU虽能提供较低的平均延迟,但除非整个系统栈都经过确定性设计,否则会因调度、中断和总线争用而产生抖动。FPGA则能以可预先限定的时序执行逻辑运算。若测试关注最坏情况下的时序表现,抖动问题比平均速度更为关键。

I/O时序常成为隐性要求。 模拟与数字I/O采样必须与求解器步长同步,若需验证快速保护或PWM同步性,执行器更新必须在固定时刻完成。当模型轻量且软件堆栈经过调优时,CPU系统可保持严密时序控制,但复杂模型和后台活动会增加抖动风险。FPGA I/O可实现时钟对齐,确保采样、锁存和沿检测在不同运行中保持一致。

| 如果在你的测试中这是真的 | 更安全的计算选择通常是 |

| 您的固定时间步长可在25至100微秒范围内设置,且不会隐藏故障。 | 选择CPU,因为它能让你更快地迭代,同时保留建模选项的灵活性。 |

| 您的保护逻辑每次都必须在几微秒内作出反应。 | FPGA之所以优越,是因为有界延迟胜过"平均而言较快"的时序性能。 |

| 您的输入/输出必须与PWM边沿和采样时刻紧密对齐。 | FPGA之所以采用时钟驱动I/O,是因为它能减少抖动和相位漂移。 |

| 您的验证依赖于大型网络、过滤器或多域模型。 | CPU,因为内存和浮点运算吞吐量能实现干净的扩展。 |

| 你需要混合保真度,部分内容快速呈现,部分内容则需精细刻画。 | 采用分体式CPU加FPGA设计,因为双方都能承担各自擅长的任务。 |

| 您预计模型将频繁修订,测试程序也将频繁更新。 | 先使用CPU,然后仅将时序关键部分迁移至FPGA。 |

评估开关换流器换流器的模型保真度极限

模型保真度是你在计算和时间余量上投入的预算。仿真 平均模型和相量模型,仅当时间步长可控时才能处理开关模型。 仿真专为微小时间步长下的开关级逻辑而设计,但会牺牲部分建模便利性。正确目标是选择能解答测试问题的最简模型。

开关器件的速度持续提升,这使得时序压力不断向仿真器转移。 开关过渡时间接近50纳秒 已在碳化硅器件中实现,这揭示了单个微秒行为中蕴含的丰富细节。虽然无法实时仿真 边沿,但如此高速凸显了死区时间、二极管恢复及dv/dt相关效应为何对求解器步长选择极为敏感。若您的验收标准包含峰值电流、过压跳闸或消隐时间,这些限制将迅速显现。

保真度决策也会改变您能够自信验证的内容。 平均化模型能提供简洁的控制回路调谐和功率流行为,却可能掩盖周期性故障及与电流检测相互作用的开关纹波。开关模型虽能捕捉这些效应,却可能迫使你在其他环节简化设计以赶工期。实用策略是将保真度与待评估信号相匹配,并将任何额外细节视为实时执行的风险——除非能证明其在所有工作点均保持稳定。

当模型需要灵活性时选择CPU,当模型需要确定性亚微秒级定时时选择FPGA。

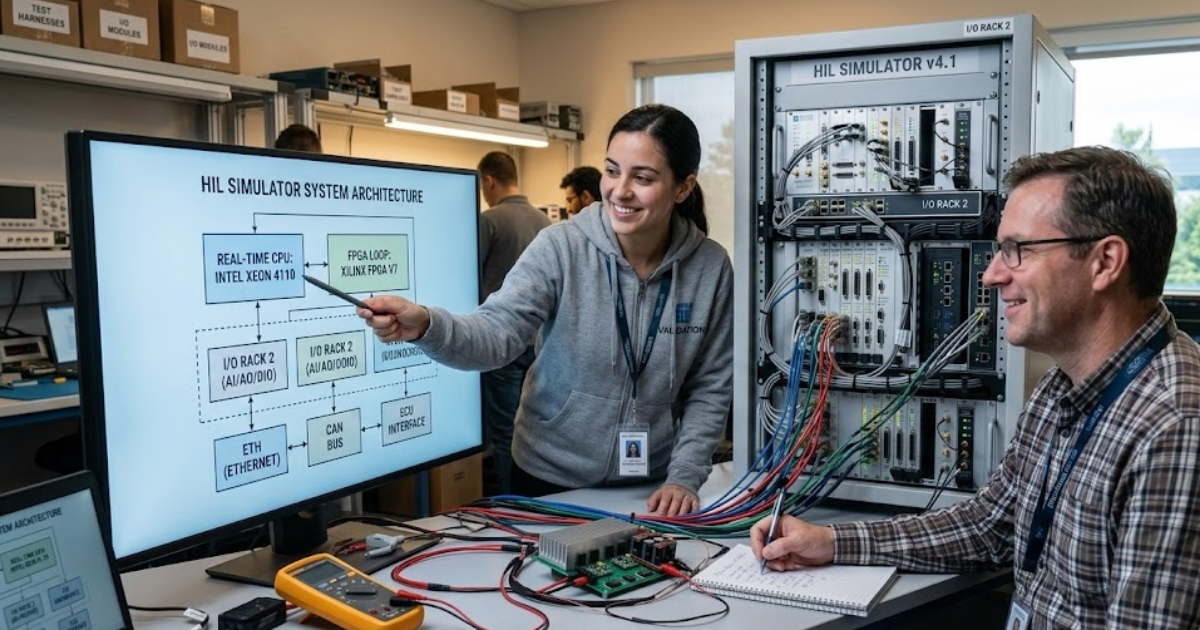

在硬件在环(HIL)设置中规划CPU与FPGA之间的任务划分

任务划分需将各项任务分配至符合其时序需求的处理器。快速切换与保护路径应部署于执行确定性的场景,而较慢的实际动态与监督逻辑则应置于建模灵活的场景。二者间的接口必须经过采样、缩放并实现精准同步。若边界处理粗糙,你将陷入看似控制问题的伪现象追查。

一个具体的模式展示了这种机制的运作方式。在验证两级并网逆变器的团队中,PWM生成、比较器式过流保护和开关级功率级可在FPGA上以亚微秒级步长运行,而电网阻抗、锁相环和功率计算则在CPU上以较大步长运行,并通过速率转换实现。 这种分工既确保了保护与开关环节所需的严苛时序精度,又为测试自动化和参数扫描保留了CPU处理余量。OPAL-RT系统常用于此类混合计算模式,因其能在单一HIL工作流中同时支持CPU和FPGA执行,无需定制化管道设计即可轻松实现跨平台工程化。

将边界规划视为I/O契约而非软件便利。明确哪些信号需穿越CPU至FPGA线路,选择明确的采样率,并定义量化与饱和处理方式。延迟必须进行端到端计数,涵盖A/D转换、求解器步进对齐及D/A更新。当你将划分视为时序架构时,便能精准定位系统中每个微秒延迟的责任归属。

核算工具链、调试及模型更新的工作量

CPU模型更新迅速,调试循环对多数工程团队而言已司空见惯。FPGA模型则需要更充分的前期规划,因为编译、资源限制和定点选择都将成为工程工作的一部分。当需要确定性时序时,这些投入将带来回报;但若过早投入过多,反而会拖慢迭代速度。分阶段实施的方法既能确保项目推进,又能锁定必须确定性的部分。

调试体验也截然不同。CPU工作流支持断点、分析器和快速重建,而FPGA工作流则更依赖断言、信号捕获以及对时序和缩放的精细验证。在CPU上微不足道的模型变更,在FPGA上可能需要重新测试数值范围、检查饱和行为并验证I/O对齐。当团队将FPGA工作视为需要形式化验证的嵌入式设计(而非临时性能补丁)时,才能获得更顺畅的结果。

- 您所需的最小时间步长及其对应的最坏情况计算余量。

- PWM、跳闸和采样保护信号的允许最大抖动值。

- 您针对定点范围、缩放和饱和度检查的方案。

- 在首个稳定基线之后,您预计的模型编辑频率。

- 您在不同测试台重现时序和数值行为的能力。

成本与进度风险通常源于工作流摩擦,而非原始计算能力。若持续添加细节直至截止日期延误,CPU工作可能无限扩张;而若初始范围过大且验证结构不足,FPGA工作则可能陷入停滞。需为时效性、保真度和I/O行为设定"完成"标准的防护栏。这种纪律性能在测试结果出现噪声时保持团队步调一致。

选择可随项目扩展的硬件在环仿真

当硬件仿真平台能助您按时完成项目、保持模型行为可追溯性、并在项目扩展时维持高迭代速度时,它便能发挥卓越价值。仅凭CPU算力无法拯救需要确定性I/O的测试平台,而仅靠FPGA的确定性也无法满足需要持续模型更新和多领域覆盖的测试平台。最佳选择通常是支持CPU与FPGA协同计算的平台,它让您无需重写所有代码即可突破技术边界。 您购买的本质是可重复执行的模型,而非特定处理器类型。

聚焦影响日常工作的几项平台特性。确定性I/O时序、清晰的速率转换处理以及可靠的同步工具,这些每周都至关重要。硬件模块化至关重要,因为通道数量和传感器类型往往会随着项目扩展而增加。软件开放性同样重要,因为团队需要连接MATLAB、Python、测试序列器和数据管道,而封闭式架构会将简单的集成变成复杂项目。

优秀的工程判断体现在如何确保仿真器长期保持准确性。应尽早锁定时序预算,仅在影响通过/失败结果时才增加仿真精度。 保持CPU模型的灵活性以支持学习过程,同时让FPGA模型专注于确定性不可妥协的关键环节。当同一测试平台需同时支持两种计算类型时,OPAL-RT完美契合这种"执行优先"的理念——您可将FPGA视为精密时序工具,将CPU作为迭代工具,而非强迫单一平台承担双重任务。

EXata CPS 专为实时性能而设计,可通过任何规模的通信网络层和连接任何数量的设备进行 HIL 和 PHIL 仿真,从而对电力系统的网络攻击进行研究。这是一个离散事件仿真 工具包,考虑了所有会影响网络(有线或无线)行为的固有物理属性。