Skalierung von akademischen HIL-Konfigurationen hin zu industriellen Validierungsplattformen

Simulation

03.03.2026

Wichtigste Erkenntnisse

- Stellen Sie zunächst die Zuverlässigkeit von HIL durch deterministisches Timing und verifizierte I/O sicher, da Rechenleistungserweiterungen allein keine vertrauenswürdigen Ergebnisse gewährleisten.

- Erweitern Sie die Kapazitäten in kontrollierten Schritten, die die Stabilität der Modelle und Arbeitsabläufe gewährleisten, indem Sie modulare Rechenkapazitäten und modulare I/O nutzen und nach jeder Änderung klare Abnahmetests durchführen.

- Betrachten Sie die industrielle Validierung als ein Nachweissystem mit automatisierten Durchläufen, Versionskontrolle und Rückverfolgbarkeit von der Anforderung bis zum Testprotokoll.

Sie können ein HIL-Labor einer Universität für die industrielle Validierung ausbauen, ohne von vorne beginnen zu müssen.

Ein häufiges Fehlermuster besteht darin, zunächst in Rechenleistung zu investieren und erst später festzustellen, dass das fehlende Puzzlestück deterministische I/O, Signalaufbereitung oder Testautomatisierung war. Eine NIST-Studie schätzt, dass unzureichendeTests die US-Wirtschaft jährlich 59,5 Milliarden DollarTests . Dieselbe Kostenlogik gilt auch für HIL, wenn spät erkannte Testfehler Neudesigns, erneute Tests und Terminverschiebungen erzwingen.

„Der Wandel ergibt sich daraus, dass man seine Testumgebung weniger als Demonstrationsplattform, sondern vielmehr als Testinfrastruktur betrachtet – mit strenger Zeitkontrolle, wiederholbarer Ausführung und nachvollziehbaren Ergebnissen.“

Die praktische Erkenntnis ist einfach: Bei HIL in Industriequalität geht es weniger um „mehr Leistung“ als vielmehr um präzises Timing, Schnittstellen und Nachweise. Sie erzielen bessere Ergebnisse, wenn Sie definieren, was „glaubwürdig“ für Ihr zu testendes Gerät bedeutet, und dann schrittweise skalieren, wobei Sie Ihre bestehenden Modelle und Laborkompetenzen schützen. Sie können weiterhin mit einem FPGA-Simulator der Einstiegsklasse beginnen, solange der Weg zu strengerem Determinismus und größeren I/O offen I/O . Diese Denkweise verwandelt ein akademisches HIL-System in eine Plattform, der Industrieteams vertrauen können.

Was ein FPGA-Echtzeitsimulator für Einsteiger bietet

Ein FPGA-Echtzeitsimulator der Einstiegsklasse bietet Ihnen deterministisches Timing und hardware I/O die Komplexität eines vollständigen Validierungsracks. Er führt Teile eines Modells auf einem FPGA aus, sodass die Schrittzeit auch unter Last konstant bleibt. Außerdem sorgt er für I/O mit geringer Latenz, wodurch Regelkreise stabil bleiben. Sie sollten ihn als Timing-Referenzpunkt betrachten und nicht nur als schnelleren Computer.

Achten Sie auf drei grundlegende Funktionen. Erstens sollte der Simulator die Ausführung mit festem Schrittweite unterstützen, wobei die Grenzen klar definiert und überprüfbar sein müssen, einschließlich des Verhaltens bei Spitzenauslastung der CPU und I/O . Zweitens sollte er direkten Zugriff auf gängige analoge und digitale I/O bieten, deren Aktualisierungsraten und Latenzzeiten bekannt sind. Drittens sollte er einen Arbeitsablauf unterstützen, der es Studierenden und Forscher:innen ermöglicht, Forscher:innen vertraute Modellierungswerkzeuge zu nutzen, während Sie während der Ausführung Echtzeitbeschränkungen durchsetzen.

Der Kompromiss im Einstiegsbereich besteht darin, dass man in der Regel zwar genügend Determinismus für die Steuerungsentwicklung erhält, jedoch nicht genügend I/O , Signalaufbereitung oder Fehlerabdeckung für eine ernsthafte Validierung. Das ist zu Beginn in Ordnung, wenn man die Plattform als Baustein betrachtet. Der Fehler besteht darin, anzunehmen, dass der erste funktionierende Regelkreis auch eine gültige Verifikationsumgebung darstellt, da die Anforderungen an Timing, Skalierbarkeit und Rückverfolgbarkeit stark ansteigen, sobald externe Partner sich auf Ihre Ergebnisse verlassen.

Erfassen Sie Lücken im akademischen HIL-System hinsichtlich zeitlicher Genauigkeit und I/O

Eine Lückenanalyse sollte mit der zeitlichen Genauigkeit und I/O beginnen, da beide Faktoren darüber entscheiden, ob Ihre simulierte Anlage und das zu testende Gerät im Gleichlauf bleiben. Die zeitliche Genauigkeit umfasst Schrittweite, Jitter und Latenz von der Berechnung bis hin zu Aktualisierungen auf Pin-Ebene. I/O umfasst Messbereiche, Auflösung, Isolation, Erdung und das Verhalten von Signalen bei der Einleitung von Fehlern. Industrial Tests , dass diese Eigenschaften messbar und stabil sind – und nicht nur „an den meisten Tagen gut genug“.

Erstellen Sie Ihre Lückenanalyse auf der Grundlage dessen, was Ihr Test nachweisen soll, und arbeiten Sie sich dann rückwärts zu den Plattformfunktionen vor. Tests zur Regelstabilität Tests ein präziseres, wiederholbares Loop-Timing und I/O deterministische I/O . Die Leistungselektronik erfordert ein Schaltverhalten mit höheren Schaltfrequenzen und sorgfältig verwaltete analoge Signalwege, einschließlich Anti-Aliasing-Filterung und sauberer Referenzspannungen. Vernetzte Steuerungen erfordern eine hohe Genauigkeit beim Protokoll-Timing, Zeitstempelung und realistische Busauslastung, da sich subtile Planungsfehler bis zur Integration verbergen können.

| Ein messbarer Meilenstein | Was ein typisches Universitätslabor bietet | Was bei der industriellen Validierung erwartet wird |

| Schrittzeitstabilität unter Spitzenlast | Funktioniert bei einfachen Konfigurationen, verschlechtert sich jedoch mit zunehmender Modellkomplexität | Ausführung mit festem Schritt und begrenzter Abweichung, die Sie melden können |

| I/O vom Rechenprozess bis zur Pin-Aktualisierung | Für Demos geeignet, selten charakterisiert | Dokumentierte Latenz mit konsistentem Timing über alle Kanäle hinweg |

| Signalintegrität in analogen Signalwegen | Grundlegende DAQ-Verkabelung, begrenzte Isolierung | Auf das Prüfobjekt abgestimmte Maßnahmen zur Isolierung, Filterung und Erdung |

| Verhalten bei der Fehlerinjektion | Manuelle Umschaltfunktionen und Ad-hoc-Skripte | Wiederkehrende, protokollierte Fehler mit gesteuertem Zeitablauf und Rücksetzung |

| Wiederholbarkeit der Tests über verschiedene Sitzungen hinweg | Das hängt davon ab, wer das Labor leitet und was sich geändert hat | Versionsverwaltete Modelle, Parametersätze und automatisierte Ausführungsprotokolle |

Dieser Schritt der Bestandsaufnahme verhindert ein häufiges Missverständnis: „Timing-Probleme“ äußern sich oft in Form von Regelungsinstabilität, doch die eigentliche Ursache können Fehler I/O , verrauschte Referenzsignale oder nicht synchronisierte Takte sein. Sobald Sie die Lücke in messbaren Größen benennen können, können Sie genau das kaufen oder entwickeln, was sie schließt. Das bewahrt Sie auch davor, zu viel in Rechenleistung zu investieren, wenn die Grenze in der Qualität der elektrischen Schnittstelle liegt.

Wählen Sie Upgrade-Schritte, die sich skalieren lassen, ohne bestehende Arbeitsabläufe zu stören

Die Skalierung funktioniert am besten, wenn Sie das beibehalten, was bereits einen Mehrwert schafft, und dann Funktionen in einer Reihenfolge hinzufügen, die den Bedarf an erneuten Tests verringert. Beginnen Sie mit zeitlicher Determiniertheit und I/O und gehen Sie dann zu Automatisierung und Rückverfolgbarkeit über. Halten Sie die Modellschnittstellen stabil, damit die Labore sie nicht jedes Semester neu schreiben müssen. Behandeln Sie jedes Upgrade als kontrollierte Änderung mit Abnahmeprüfungen und nicht als einmalige Umrüstung.

Verwenden Sie eine kleine Reihe von Upgrade-Schritten als wiederverwendbares Playbook und verknüpfen Sie jeden Schritt mit einem messbaren Ergebnis, das Sie innerhalb eines Tages überprüfen können. So bleibt das Labor für Lehrzwecke nutzbar, während gleichzeitig die Anforderungen an die Validierung gegenüber Partnern erhöht werden. Außerdem erleichtert dies die Budgetplanung, da jeder Schritt eine klare Definition dessen enthält, wann er als „abgeschlossen“ gilt, und einen offensichtlichen nächsten Schritt vorsieht, falls Sie mehr Kapazität benötigen. Die folgende Liste hat sich bewährt, da sie den Kauf hardware vermeidet, hardware noch nicht anhand von Testergebnissen rechtfertigen können.

- Bestimmen Sie die Taktsynchronisation, den Jitter und I/O Ihres Stromkreises mit einem wiederholbaren Test.

- Stellen Sie zunächst I/O analogen und digitalen I/O sicher, indem Sie geeignete Messbereiche, Isolierung und Erdung verwenden.

- Fügen Sie eine deterministische FPGA-Ausführung für die Teile des Modells hinzu, die zeitliche Grenzen festlegen.

- Standardisieren Sie die Modellpaketierung und die Parameter, damit die Ausführungen für alle Benutzer reproduzierbar sind.

- Automatisieren Sie die Ausführungssteuerung und Protokollierung, damit jedes Ergebnis eine eindeutige Herkunftsnachverfolgung aufweist.

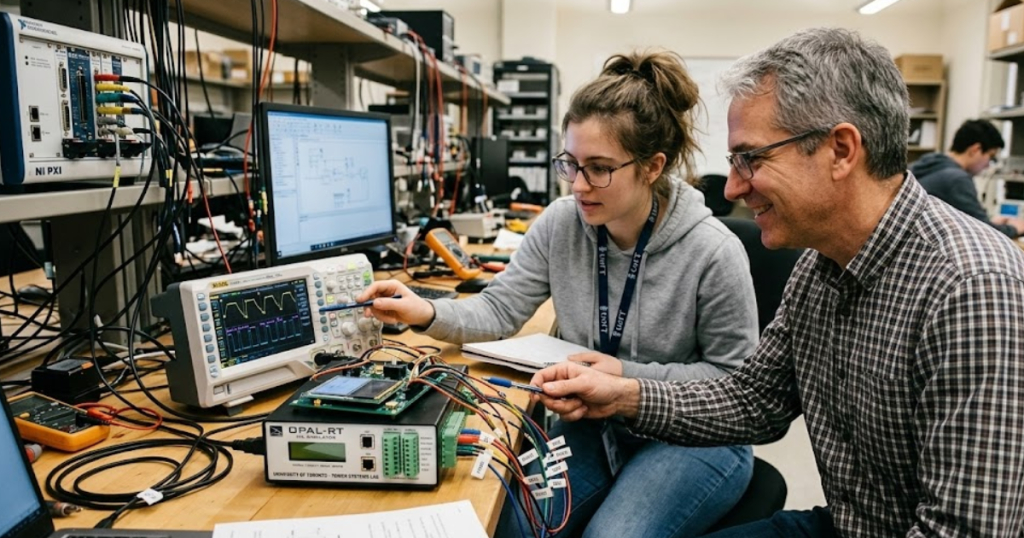

Ein praktisches Umsetzungsmodell besteht darin, Ihre bestehenden Modelle und Laborskripte beizubehalten und sie dann einer strengeren Ausführungssteuerung zu unterwerfen, während Sie deterministische Rechenkapazitäten und I/O verbesserte I/O hinzufügen. Plattformen von OPAL-RT werden häufig auf diese Weise in Labors eingesetzt, die den Übergang von der Universität zur Industrie erleichtern, da sie modulares Wachstum unterstützen und sich dabei auf die Echtzeitausführung konzentrieren, anstatt auf benutzerdefinierten Glue-Code. Allerdings zahlt sich die Plattform nur dann aus, wenn Ihr Labor die Disziplin an den Tag legt, Timing-Werte zu messen, Konfigurationen zu fixieren und die Reproduzierbarkeit der Ergebnisse sicherzustellen.

„Die sinnvollste Änderung der Denkweise besteht darin, langweilige Beständigkeit gegenüber cleveren Einzelaktionen zu bevorzugen.“

Entwicklung einer modularen Plattform für Skalierbar -Simulationen

Dank des modularen Aufbaus können Sie Rechenleistung und I/O skalieren – genau das sollteSkalierbar in der Praxis bedeuten. Die Skalierung der Rechenleistung umfasst die Modellgröße, die Auslastung des Solvers und die Aufteilung auf Prozessoren oder FPGA-Ressourcen. I/O umfasst die Anzahl der Kanäle, die Signaltypen und die Anforderungen an physikalische Schnittstellen, wenn sich die Geräte weiterentwickeln. Dank der Modularität müssen Sie das Labor nicht jedes Mal neu aufbauen, wenn bei einem Projekt ein weiterer Wandler, ein weiterer Sensorsatz oder ein weiterer Bus hinzukommt.

Beginnen Sie mit einer klaren Trennung zwischen drei Schichten: Rechen-, Schnittstellen- und Orchestrierungsschicht. Die Rechenschicht sollte die Echtzeitausführung mit vorhersehbarer Leistung und klaren Zeitvorgaben übernehmen. Die Schnittstellenschicht sollte sich um die komplexen Details der physikalischen Ebene kümmern, einschließlich Isolierung, Signalaufbereitung und Protokollschnittstellen, ohne dass eine Neuprogrammierung der Modelle erforderlich wird. Die Orchestrierungsschicht sollte die Laufsteuerung, Parametrierung, das Verhalten bei einem Reset und die Protokollierung übernehmen, damit sich die Tests über alle Benutzer und Zeiträume hinweg einheitlich verhalten.

Bei der Synchronisation und Integration treten Kompromisse auf. Simulationen mit mehreren Knoten, verteilte I/O und Netzwerksynchronisation führen zu Problemen bei der Taktabstimmung, die ein kleines Labor ignorieren kann, bis die Ergebnisse über verschiedene Sitzungen hinweg voneinander abweichen. Planen Sie Zeit für Timing-Prüfungen auf Systemebene ein, nicht nur für die Modellkorrektheit. Eine modulare Plattform ist dann erfolgreich, wenn Sie Kapazitäten hinzufügen können, ohne dabei die Testabsicht und den Nachweispfad zu verändern.

Erfüllen Sie die Anforderungen der industriellen Validierung durch wiederholbare Tests und Rückverfolgbarkeit

Bei der industriellen Validierung müssen Sie nicht nur nachweisen, dass ein Test durchgeführt wurde, sondern auch, dass er jedes Mal auf dieselbe Weise ablief und dass das Ergebnis auf eine Anforderung zurückgeführt werden kann. Wiederholbarkeit wird durch kontrollierte Konfiguration, deterministische Ausführung und automatisierte Protokollierung gewährleistet. Rückverfolgbarkeit entsteht durch die Verknüpfung von Modellversionen, Parametersätzen, Firmware-Versionen und Test-IDs mit jedem Durchlauf. Ohne diese Kette wird es schwierig sein, extern Vertrauen in Ihr noch so überzeugendes technisches Ergebnis zu gewinnen.

Die Wahl des Forschungsgebiets ist entscheidend, da das menschliche Gedächtnis und spontane Laboraufzeichnungen nicht ausreichen. Eine Umfrage von Nature ergab, , dass 70 % der Forscher:innen versucht haben, die Experimente anderer Wissenschaftler*innen zu reproduzieren, und dabei gescheitert sind. Dasselbe Reproduzierbarkeitsproblem tritt auch in der HIL auf, wenn ein Controller-Update, eine Parameteranpassung oder eine zeitliche Änderung die Ergebnisse unbemerkt verändert. Bei soliden Validierungsverfahren wird jeder Durchlauf als Datensatz und nicht als einmaliges Ereignis behandelt.

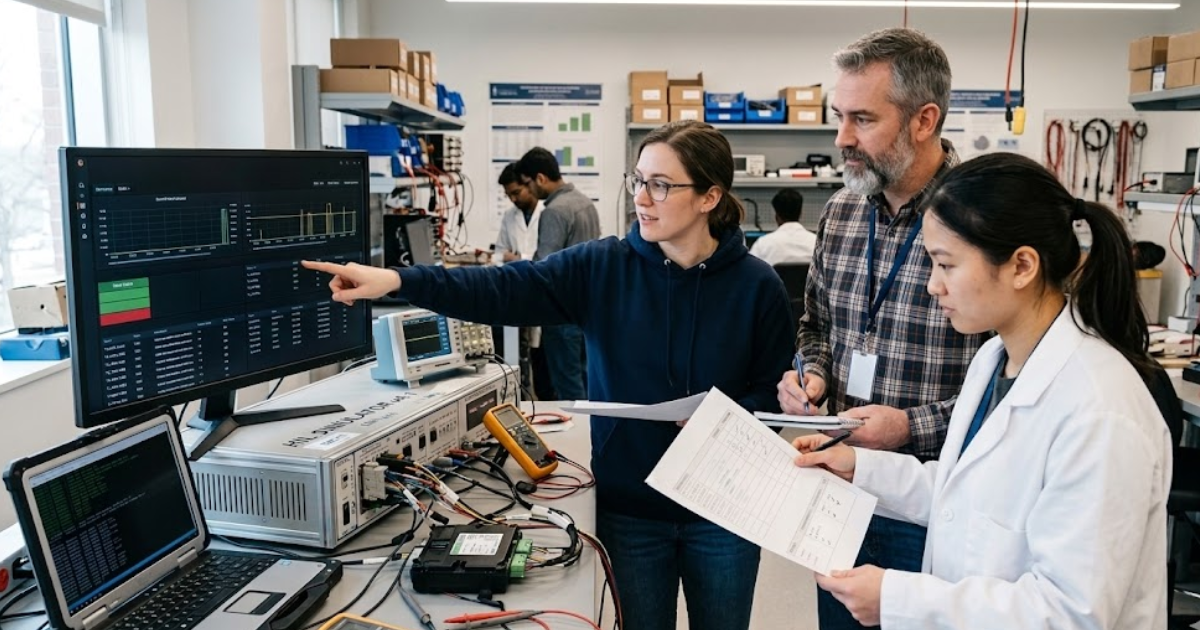

Ein konkreter Arbeitsablauf veranschaulicht den Sprung vom akademischen Proof-of-Concept zur industriellen Einsatzreife: Ihr Labor validiert eine Steuerung für einen elektrischen Antriebsumrichter hinsichtlich einer Überstromanforderung, indem es eine skriptgesteuerte Sequenz ausführt, die Drehmomentbefehle durchläuft, zu einem bestimmten Simulationszeitpunkt einen Kurzschlussfehler einspeist und sowohl I/O als auch den Zustand der Steuerung protokolliert. Der Test erreicht Industriestandard, wenn der Durchlauf automatisch die genaue Modellversion, die FPGA-Bitstream-Version, den Hash der Parameterdatei, die Firmware-Version und die Bestehens-/Durchfallkriterien erfasst und anschließend auf einem anderen Prüfstand mit derselben Konfiguration das gleiche Ergebnis liefert. Dieses Maß an Kontrolle macht eine HIL-Konfiguration zu einer verlässlichen Validierungsressource, selbst wenn sich das Personal wechselt und Projekte ändern.

Vermeiden Sie häufige Fehler bei der Skalierung beim Übergang vom Labor in die Produktion

Die meisten Probleme bei der Skalierung entstehen dadurch, dass industrielle Tests „mehr vom Gleichen“ betrachtet werden, anstatt sie als einen anderen Evidenzstandard zu betrachten. Zu den häufigsten Fehlern zählen der Kauf von Rechenleistung, bevor I/O sichergestellt ist, das Verlassen auf manuelle Testausführung und das Unbeachtetlassen von Timing-Abweichungen. Ein weiterer häufiger Fehler ist die Vermischung von Schulungskonfigurationen mit der Validierung durch Partner, ohne dass eine klare Trennung der Konfigurationen vorgenommen wird. Die spätere Behebung dieser Probleme kostet doppelt Zeit: einmal durch Nacharbeiten und ein weiteres Mal durch den Verlust des Vertrauens.

Leitplanken unterstützen dem „heroischen Debugging“. Legen Sie eine kleine Auswahl an Referenztests fest, die nach jeder Änderung bestanden werden müssen, und verlangen Sie im Rahmen dieser Überprüfung Zeit- und I/O . Halten Sie eine klare Grenze zwischen experimentellen und validierten Modellen ein, auch wenn beide im selben Labor betrieben werden. Planen Sie die Wartbarkeit ein, denn ein Labor, das nur von einer Person betrieben werden kann, gerät ins Stocken, sobald die Zeitpläne enger werden.

Der sinnvollste Umdenkprozess besteht darin, langweilige Beständigkeit gegenüber cleveren Einmalaktionen zu bevorzugen. Wenn Ihr Team denselben Test im nächsten Monat erneut durchführen und das gleiche Ergebnis erzielen kann, werden Partner den Ergebnissen vertrauen und die Schüler die richtigen Gewohnheiten erlernen. OPAL-RT kann diese Art der disziplinierten Ausführung unterstützen, aber der entscheidende Faktor wird immer sein, wie Ihr Labor Akzeptanzkriterien definiert, Änderungen kontrolliert und Timing sowie I/O messbare technische Artefakte behandelt. Das ist es, was Skalierung zu einer dauerhaften Fähigkeit macht, anstatt zu einem Zyklus von Neuaufbauten.

EXata CPS wurde speziell für die Echtzeit-Performance entwickelt, um Studien von Cyberangriffen auf Energiesysteme über die Kommunikationsnetzwerkschicht beliebiger Größe und mit einer beliebigen Anzahl von Geräten für HIL- und PHIL-Simulationen zu ermöglichen. Es handelt sich um ein Toolkit für die diskrete Ereignissimulation, das alle inhärenten physikalischen Eigenschaften berücksichtigt, die sich auf das Verhalten des (drahtgebundenen oder drahtlosen) Netzwerks auswirken werden.