核心要点

- 仅在验证确定性时序(包括负载下的最坏情况循环延迟和抖动)后,才进行硬件在环(HIL)测试。

- 匹配植物模型的保真度、求解器选择以及传感器执行器的非理想特性,使其与控制器的敏感点相匹配,而非追求图表上的美观效果。

- 通过规范的集成控制措施保障测试可信度,包括:统一的信号契约、自动化的可重复运行以及严格的版本追溯机制。

大多数硬件在环(HIL)测试失败并非源于某个重大失误,而是由细微的不匹配逐渐累积而成——这些不匹配在时序、模型保真度和集成细节中不断叠加,最终导致测试平台难以信赖。一旦出现这种情况,团队要么通过昂贵的实验室工作过度修正,要么带着本以为已被HIL覆盖的漏洞发布产品。

一套规范的硬件在环仿真 可避免这种恶性循环。并非所有环节都需要完美无缺,但必须明确哪些环节必须精确、哪些环节可近似处理,并通过可重复的检测手段验证差异。以下陷阱聚焦于最常破坏嵌入式系统和控制验证的故障模式。

“只有当时序、模型和接口与目标系统完全匹配时,硬件在环测试才能建立信心。”

在进行任何布线之前,请先设定明确的硬件在环测试目标

硬件在环技术将真实控制器与仿真被控对象相连,使您能够安全且可重复地测试闭环行为。通往可靠结果的最快路径始于明确的时序目标、接口规范和验收标准——这些选择将决定模型的保真度、I/O硬件配置,以及您对每次通过或失败结果的解读方式。

在讨论工具或模型细节之前,先定义何为"良好"。这一简单步骤能防止团队为获得期望结果而"调整设备",从而确保验证的是实际计划交付的控制系统。

- 控制带宽和采样时间目标

- 输入/输出范围、负载及隔离需求

- 网络协议与时序容差

- 与要求相关的合格/不合格判定标准

- 模型与测试脚本的可追溯性

硬件在环测试的9大陷阱及解决方案

硬件在环测试集群的常见问题可归纳为三大主题:非确定性时序、无法真实反映控制器"感知"的模型,以及悄然扭曲信号的集成环节。将每个陷阱视为可提前验证的检查点——在扩大测试覆盖范围或开始追查控制器缺陷之前,务必先行验证。

1. 因步长和I/O延迟导致的时序预算超出

在嵌入式系统中,当控制器的预期采样时序与仿真器的步长加I/O及驱动延迟不匹配时,HIL仿真会失败。解决方法是将时序视为需测量的预算而非预设参数:锁定固定步长的调度计划,随后在负载条件下验证端到端环路延迟与抖动。

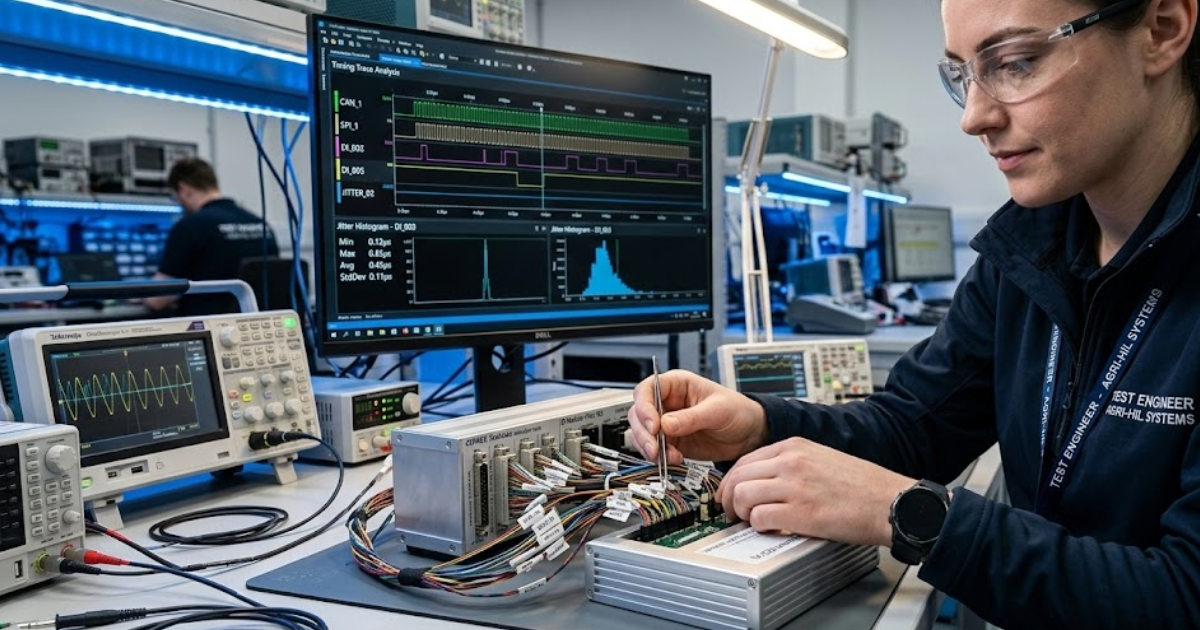

延迟常潜藏于团队忽视之处:ADC与DAC转换、协议栈及主机CPU争用。实时执行追踪应呈现最坏情况下的步进超时与I/O更新延迟,而非仅显示平均值。使用OPAL-RT等平台时,需依托确定性调度与仪器监测来验证时序预算始终处于控制器容差范围内。

2. 植物模型保真度过低,导致控制器带宽不足

在低频下看似稳定的模型,可能在控制器带宽范围内毫无用处——此时延迟、谐振和饱和效应会重塑稳定裕度。解决方法是:将模型保真度与控制目标匹配,然后在控制器将激发的频率下验证模型响应。保留影响相位和增益的高频动态特性。

保真度不等同于复杂度。在保留主导闭环行为的快速电气或液压动态特性时,通常可剔除低速热力或机械细节。可行的验证方法是:将频率响应或阶跃响应与可信基准进行对比,随后快速执行敏感性分析,以确定哪些参数会影响通过或失败的结果判定。

3. 求解器与离散化方案的选择会导致混叠与不稳定现象

求解器设置可能在虚假振荡中引入能量、消除阻尼或产生混叠切换效应。解决方法是选择与系统物理特性和实时步长匹配的求解器及离散化方案,并通过应力工况验证数值稳定性。采样频率过低会将真实的高频成分转化为误导性的低频行为。

混叠现象常表现为“控制器不稳定”,但在台架测试中却消失无踪。需重点关注突变点、开关市场活动及传输延迟,并选择在固定步长执行下行为可预测的建模方法。当被控对象包含快速开关或刚性动力学时,需采用更小的步长、更换求解器或设置专用计算路径,以确保仿真 。

4. 信号缩放与电信号调理误差导致测量结果失真

错误的缩放和调理会悄无声息地破坏结果,因为控制器仍在运行,且图表看起来依然合理。通过为每个通道制定严格的信号契约来解决此问题:包括单位、缩放、极性、偏移、滤波及预期噪声。在运行复杂场景前,需通过环回检测和已知注入值验证契约有效性。

电气细节与数学计算同样重要。输入阻抗、传感器激励、隔离、接地及共模限制都可能导致测量失真或保护装置误动作。若您的硬件在环系统采用信号调理,请将其视为装置的一部分——因为它改变了控制器所"感知"的信号。为每个通道建立清晰的校准记录,可为您节省数日的调试时间。

5. 协议集成可隐藏抖动、数据包丢失和重传现象

网络化I/O在功能层面看似正常,却可能存在时效性故障,尤其当重试机制和缓冲区掩盖了延误的时限时。解决方法是:在最恶劣的总线负载条件下测量消息年龄、抖动和丢失率,然后将控制器的预设条件调整为与网络实际传输能力相匹配。确保每条消息都关联可审计的时间戳。

集成问题往往超出控制团队的视野范围,存在于网关固件、驱动程序或交换机配置中。将协议配置视为验证环节而非实验室基础工作。当发现间歇性故障时,需在接口两端同步捕获跟踪数据,以区分控制器时序问题与网络传输问题。

6. 硬件在环测试台与目标硬件之间的接口不匹配

当仿真被控对象通过与生产系统不匹配的接口连接时,HIL测试将失效。解决方法是:通过与实际运行环境相同的电气和协议路径测试控制器,或详细记录所有不匹配项及其对延迟、分辨率和故障行为的影响。

一个具体案例揭示了这种情况如何出错:在实验室友好的以太网桥上经过验证的电机控制器,可能通过所有功能测试,但一旦迁移到生产总线就会失效——因为仲裁延迟和消息时序会改变实际的环路延迟。一个简单的缓解方案是在早期进行"生产路径"检查点测试,即使工厂模型仍处于粗略阶段。

“一张通行证只有在你日后能再次使用时才真正重要。”

7. 传感器与执行器仿真存在限值、噪声及延迟缺失

理想的传感器和执行器会使控制器表现得比实际更优异。要解决这个问题,需建模那些塑造控制行为的非理想特性:量化误差、偏置、漂移、噪声色、死区、速率限制和传输延迟。将这些非理想特性与实际硬件和布线引入的偏差相匹配,而非与理想化的要求相匹配。

在瞬态、故障和极限工况下,限值最为关键——这正是硬件在环仿真(HIL)应发挥保护作用的场景。若执行器模型永不饱和,则无法观察到积分器饱和效应或恢复动态;若传感器模型无延迟,则会低估相位滞后并高估稳定裕度。请将这些视为测试输入,而非事后补充。

8. 测试自动化缺口降低了跨团队的可重复性和覆盖率

手动HIL运行产生的结果无法复现、比较或论证。通过脚本化测试执行、种子随机性噪声、确定性初始条件及自动化伪像捕获来解决此问题。自动化无需复杂,但必须确保每次运行在不同人员、不同日期及不同实验台之间具有可比性。

可重复性在于区分控制器调试与测试平台调试的差异。每次运行时都需存储日志、时序追踪、仿真器配置及控制器构建标识符。当回归问题出现时,您将能快速回答一个基本问题:是系统发生了变化,还是测试方案发生了变化?

9. 配置与版本漂移导致测试结果可追溯性中断

当模型版本、参数集、固件构建和校准文件在缺乏可追溯性的情况下发生漂移时,HIL测试的可信度将崩溃。通过实施受控的配置流程来解决此问题,该流程需将每个测试结果与精确的模型版本、二进制文件、工具链及I/O映射关联起来。只有当测试结果可被复现时,其通过才具有意义。

漂移现象还会制造虚假故障,消耗资深工程师的宝贵时间。锁定参数来源,采用统一命名规范,并建立通道映射与缩放的单一数据源。当团队共享设备时,轻量级的变更控制机制能防止"微调"演变为验证签核阶段长达数周的混乱局面。

| 陷阱 | 主要收获 |

|---|---|

| 因步长和I/O延迟导致的时序预算超出 | 测量环路延迟和抖动,然后强制执行固定的时序预算。 |

| 植物模型保真度过低,无法满足控制器的带宽要求 | 将影响相位和增益的动态特性控制在带宽范围内。 |

| 求解器和离散化选择会产生混叠和不稳定性 | 选择在固定步长下保持稳定且避免混叠的求解器。 |

| 信号缩放与电信号调理误差导致测量结果失真 | 为每个I/O通道采用严格的单位和缩放协议。 |

| 协议集成可隐藏抖动、丢包和重传 | 为消息添加时间戳,并在最坏情况总线负载下测试时序。 |

| HIL测试台与目标硬件之间的接口不匹配 | 通过生产接口路径进行验证,或量化每个不匹配项。 |

| 传感器和执行器仿真忽略了极限值、噪声和延迟 | 添加非理想性,使瞬态和故障行为与物理系统相匹配。 |

| 测试自动化缺口导致跨团队的可重复性和覆盖率降低 | 自动化运行并捕获工件,使回归测试具有可验证性。 |

| 配置和版本漂移破坏了测试结果的可追溯性 | 将每个结果与确切的型号、固件和校准版本关联起来。 |

优先处理时效性、保真度和集成性检查,以加快审批流程

时序、保真度和集成度是区分可靠HIL测试与昂贵表演的三大关键指标。首先确保确定性时序,其次在控制器敏感区域提升被控对象模型的精度,最后锁定接口以确保信号传递符合预期。遵循此顺序可避免为匹配缺陷测试台而"修正"控制器的错误。

一旦这些基础稳定后,更广泛的测试覆盖就值得投入精力,因为测试失败指向控制系统而非设置问题。将硬件在环(HIL)视为规范化工程工作流的团队——包括使用OPAL-RT测试台的团队——往往能更快推进工作,因为当利益相关方询问测试结果如何产生及实际证明了什么时,每个测试结果都能经得起推敲。

EXata CPS 专为实时性能而设计,可通过任何规模的通信网络层和连接任何数量的设备进行 HIL 和 PHIL 仿真,从而对电力系统的网络攻击进行研究。这是一个离散事件仿真 工具包,考虑了所有会影响网络(有线或无线)行为的固有物理属性。