A practical HIL workflow for validating SiC traction inverters

Power Systems

01 / 25 / 2026

Key Takeaways

- Treat inverter HIL testing as the primary gate for control stability and protection behaviour, then use bench work to confirm.

- Choose HIL model fidelity based on what triggers trips and changes control choices, not on the most detailed model available.

- Lock proof points and pass conditions early so every software and hardware change stays measurable and repeatable.

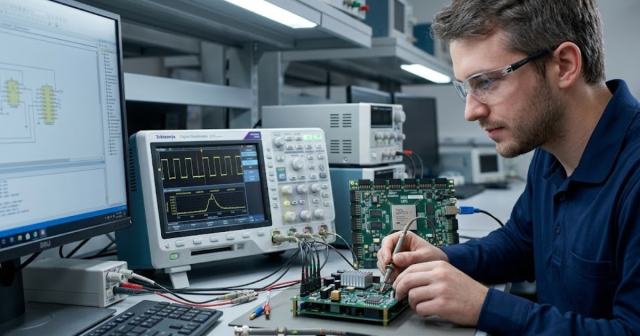

You will validate a SiC traction inverter faster when HIL testing is the main gate for control and protection behaviour. SiC switching speed and high dv/dt expose timing and protection mistakes. HIL lets you find those gaps on a repeatable bench while your control code runs unchanged. Electric car sales neared 14 million in 2023, reaching 18% of all cars sold.

SiC traction inverter validation is a chain of proofs, not a single dyno run. Each proof must hold as you move from models to power hardware. HIL forces repeatability before volts and amps are on the table. A tight HIL workflow will make later bench work boring.

What validation must prove for SiC traction inverter readiness

Readiness means you can prove torque control stays stable and protection acts safely across the operating limits. Current, voltage, and temperature corners must be covered, not implied. Trips must be fast and selective, with clear latching rules. Recovery must also be safe, so the inverter does not restart into the same fault.

A representative proof starts with a 0 to 250 N·m torque step at 800 V DC near base speed. It then flips into regen and checks current loop stability and DC bus control. Another run injects a current sensor offset and checks the plausibility trip and diagnostic flag. A final run forces a bus overvoltage and verifies clamp action and shutdown timing.

SiC makes small delays and measurement errors matter. Deadtime, sample phase, and quantization will shift torque and trip points. High dv/dt coupling will pollute current feedback and cause false overcurrent. Pass conditions tied to requirements will stop one-off successes from passing review.

Why HIL testing anchors inverter validation strategy

“HIL anchors inverter validation because it runs your controller at speed while the plant stays safe and repeatable.”

You will see how IO delays, quantization, and signal noise affect control behaviour. Faults can be injected at exact instants and repeated until the response is understood. The same stimulus can be rerun after every build, so changes are measurable.

A timing-heavy example is a resolver dropout. The test bench can remove position feedback for 20 ms at 9,000 rpm, then restore it and verify the restart state machine. A protection example is a virtual phase-to-phase short at a known electrical angle, followed by a check of PWM disable latency. A sensing example is swept current noise that confirms filtering will not destabilize the current loop.

Repeatability changes how you use scarce bench time. Protection tuning becomes traceable instead of trial-and-error on a dyno. Root cause analysis gets faster because the same stimulus yields the same response when code is unchanged. Bench work still matters, but it becomes confirmation instead of discovery.

Where HIL fits within the full inverter validation sequence

HIL sits between early controller checks and high-power bench testing, proving logic before hardware stress. Model-in-the-loop and processor-in-the-loop catch control and timing issues. HIL validates closed-loop behaviour with realistic IO delays and fault injection. High-voltage bench work becomes safer once that suite passes.

Start with a current loop step test on a simulated machine, then run timing checks on the target CPU. Next, run HIL with the PWM capture and sensor timing used on hardware. A low-voltage power stage can then confirm gate drive protection. Full DC bus and dyno testing starts after the HIL suite passes.

Gates stop teams mixing problems that belong in different places. Modelling gaps are easier to fix before hardware noise joins the signal. Protection issues are cheaper to resolve before device stress is high. A consistent test suite supports an audit trail from requirement to verified behaviour.

| Validation gate | What you will prove | What breaks when skipped |

| Control logic | Stable steps and limits | Late oscillation on dyno |

| Timing and sampling | PWM and sensing aligned | False trips and torque ripple |

| HIL fault injection | Trips and restart match requirements | Shutdowns during transients |

| Low-voltage power stage | Gate drive reacts safely | Debugging starts at high voltage |

| High-voltage confirmation | Thermal and voltage margins hold | Margins collapse under load |

How to structure a SiC inverter focused HIL workflow

A SiC inverter focused HIL workflow starts with risk targets, not a pile of scripts. You will pick behaviours that can damage hardware or break torque delivery. You will match model fidelity and IO timing to those behaviours. Automated regression will keep those proofs stable across builds.

A workable workflow will include:

- Set operating and fault limits in writing

- Model DC link, machine, and sensor paths

- Match PWM, ADC, and communication timing

- Automate startup, step, regen, and trip tests

- Freeze pass criteria per requirement

Some teams start with regen-to-traction transitions because they mix high current and DC bus stress. Other teams start with desaturation and overcurrent because hardware protection will act before software if thresholds are wrong. Sensor plausibility also deserves early focus, since an offset can saturate the current loop. The first pick matters less than writing pass conditions before you run.

Discipline keeps scope under control. The model will not need every parasitic, but it must be accurate for the tests you run. Logging must be designed before the first run so failures can be reproduced. Regression matters more than a single run, since defects appear after small edits.

What fidelity requirements matter most for inverter HIL models

Fidelity matters only where it changes control choices or protection triggers. DC link dynamics, machine back-EMF, and sensor paths must be accurate enough that the controller behaves the same way it will on hardware. Timing and quantization effects must be represented so stability margins are honest. Switching waveforms are optional unless a test depends on ripple or sampling artefacts.

Current sampling under PWM is a good place to draw the line. Average-value models work for many control tests, but they miss ripple that causes false overcurrent. Multiphase machines add coupling that changes fault currents and torque ripple under a leg loss. OPAL-RT can run an electromagnetically coupled 12-phase PMSM model on FPGA in real time, which fits tests that depend on those phase interactions.

Loss patterns shift, which moves thermal stress and derating triggers. One WLTC-based analysis reported a 73.5% average loss reduction for a SiC inverter versus a Si IGBT inverter, and that shift will move where heat is generated. A model that ignores this will mislead thermal limits and protection thresholds. Fidelity is about matching the failure physics your tests target.

“Judgment is the difference between progress and churn.”

Common failure modes caused by weak inverter HIL validation

Weak inverter HIL validation usually misses timing, sensing, or fault logic, then problems appear once energy is high. A current loop that looks stable in slow simulation will oscillate once IO delays and sampling phase are realistic. Protection thresholds tuned on clean signals will mis-trip with noise and quantization. Recovery logic can also be fragile, causing repeat trips during restart attempts.

A common pattern is a clean dyno pull until a fast regen event, followed by a bus overvoltage shutdown. The root cause can be a DC link model that hides bus spike during torque reversals, so clamp logic is tuned too late. Another pattern is desaturation at low torque, caused by gate drive settings that were never tested under realistic dv/dt. Sensor checks fail too, passing steady state then flagging false faults during torque steps.

The cost is lost time and lost confidence in protection. Teams start tuning around trips instead of fixing the cause, and risk climbs. A tighter HIL approach will surface these behaviours under controlled stimulus, so fixes can be linked to a cause and verified. Strong tests turn late failures into repeatable bugs with clear owners.

How HIL results guide hardware and control design decisions

HIL results should change design choices, not just confirm them. A failed test tells you where the fix belongs: code, sensing, protection, gate drive, or layout. Each fix should create a regression test that will fail if the defect returns. Clear gates turn HIL into a system discipline.

An overcurrent trip that happens only during torque reversals is a useful example. Data often shows estimator saturation from sampling phase, so ADC timing shifts and observer gains adjust. Desaturation aligned with high dv/dt points to gate resistance, blanking time, and a software validity check. Restart oscillations tend to be state machine logic, and HIL proves that fast.

Judgment is the difference between progress and churn. Teams that treat every failure as tuning waste weeks, while teams that tie failures to test intent fix the right layer. OPAL-RT fits this workflow when you need deterministic HIL runs with the same timing and stimulus across builds, so changes can be evaluated. Disciplined HIL work will save you from late nights on high-voltage hardware, and it will leave you with a validation record you can stand behind.

EXata CPS has been specifically designed for real-time performance to allow studies of cyberattacks on power systems through the Communication Network layer of any size and connecting to any number of equipment for HIL and PHIL simulations. This is a discrete event simulation toolkit that considers all the inherent physics-based properties that will affect how the network (either wired or wireless) behaves.