9 Step electrification test plan checklist for powertrain and energy systems

Power Electronics, Energy

01 / 01 / 2026

Key Takeaways

- Clear operating envelopes and pass rules will prevent debates and rework later.

- Fault order and transient stress tests will expose protection gaps before hardware sessions.

- Release gates tied to repeatable HIL runs will keep changes controlled and traceable.

Your electrification test plan will keep high-voltage powertrain work safe and repeatable before hardware goes live. It defines pass and fail rules for control loops, protection, and timing. HIL lets you stress the controller while the plant stays virtual. The checklist below keeps priorities clear when tests pile up.

Global electric car sales neared 14 million in 2023, about 18% of all cars sold. More teams now ship electrified drives and energy systems. High power electronics and fast control loops create faults that desk models hide. A checklist helps you prove safety first, then tune performance.

What an electrification test plan must prove before hardware risk

Your plan must prove operating limits hold during normal use and transients. Closed-loop targets must be measurable and repeatable. Protection actions need verified triggers and responses. Simulation step timing and I/O must match what the controller expects.

Torque steps should show the current limit clamps without chatter. Bus undervoltage events should show contactors open in the right order. Sensor dropouts should push the controller into a defined fallback mode. Each expected response needs to be written before you run the test.

Rank work instead of adding everything. Protection and fault handling come before control feel. Model detail should match the decision you need to make.

“Each test should end with one action so the plan stays short.”

9-step electrification test plan checklist for powertrain HIL programs

1. Electrical architecture boundaries and operating envelopes are explicitly defined

Set limits for voltage, current, speed, torque, and temperature, and map each to a response. Make the plant clamp or trip at those boundaries so the controller never sees impossible states. Force a DC bus overvoltage and verify the torque cut rule. Clear envelopes stop debates when results look odd.

2. Control objectives and closed-loop success criteria are testable

Turn each control goal into logged signals and a pass rule that stays stable over reruns. Cover response time, stability, steady-state error, and limit behaviour. Run a pedal step and confirm target torque without sustained oscillation. Testable criteria keep subjective calls out of release gates.

3. Fault cases are prioritized by safety impact and test feasibility

List faults as you will inject them and sort by harm, likelihood, and repeatability. Start with controllable faults in HIL before rare edge cases. Include sensor stuck values, phase open-circuit, and contactor feedback disagreement. This order stresses protection and diagnostics first.

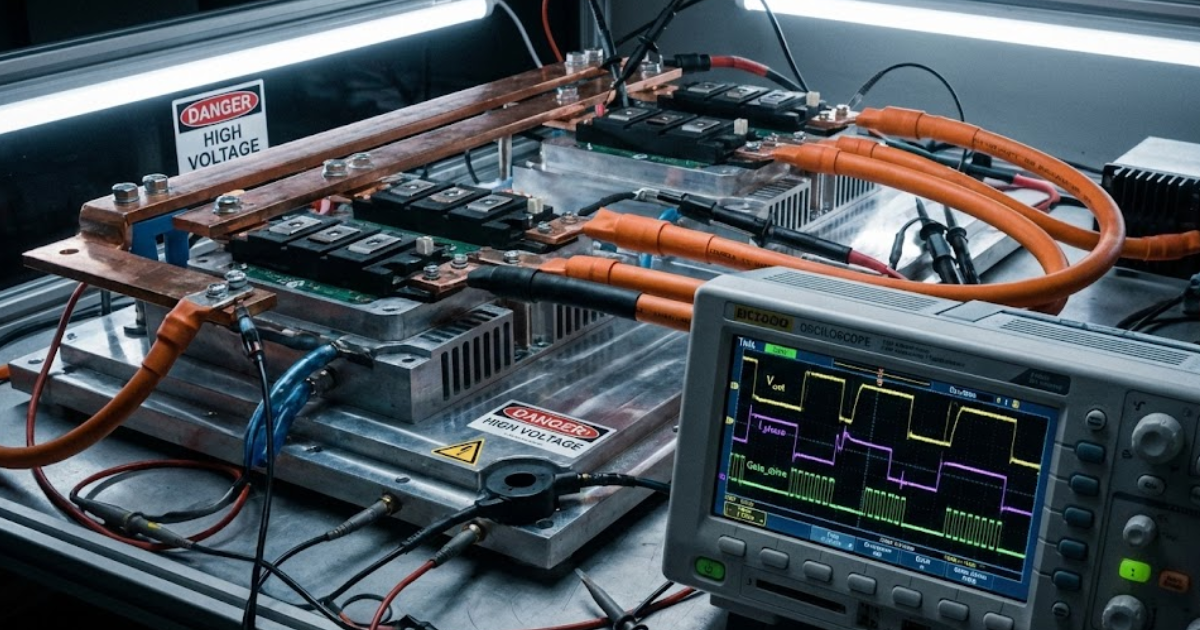

4. Power electronics behaviour is validated under transient stress

Plan around edges, not steady state, using load steps and torque reversals. Cover current limiting, PWM saturation, dead-time, and cross-conduction warnings. Run a fast regen-to-motoring transition and check DC link sag recovery. An ideal plant will hide these behaviours.

5. Electric machine models reflect thermal and electromagnetic limits

Motor models must match limits under heat and speed. Include saturation, saliency, resistance shift with temperature, and losses that move torque. Inject an open-phase fault on a multiphase PMSM and confirm current reallocation stays inside phase limits. Missing effects will mislead tuning.

6. Energy storage dynamics are exercised across realistic duty cycles

Test battery behaviour across state of charge, temperature, and power pulses, not only nominal points. Include precharge, contactors, voltage sag, and limit enforcement from the battery model. Battery pack cost was $139/kWh in 2023 for usable energy. Run cold start, a hard acceleration pulse, then regen at low state of charge.

7. Controller interfaces and HIL I/O fidelity are verified early

Interface errors look like control problems, so verify them before tuning. Check scaling, units, sign, sampling, and latency for each I/O path. Feed a known current waveform and confirm the controller reads the right value after filtering. Clean interfaces make later faults easier to interpret.

8. Real-time constraints are verified against worst-case computation load

Real-time performance is mandatory because missed steps can break closed-loop behaviour. Stress worst-case switching, logging, and fault injection, then measure step time margin and overruns. Teams using OPAL-RT can log step time and set a firm margin rule. If timing fails, the plan must name what gets simplified or moved to FPGA.

9. Test results map directly to design decisions and release gates

Each test ends with an action: accept, fix, or re-scope the requirement. Store results with configuration details so reruns answer the same question. Block a software build if a protection path does not trigger the expected shutdown. Traceable gates keep HIL from becoming a folder of plots.

| Step you will run | Outcome you will trust |

| 1. Electrical architecture boundaries and operating envelopes are explicitly defined | You will map limits to actions and avoid impossible states. |

| 2. Control objectives and closed-loop success criteria are testable | You will score control quality with logs and pass rules. |

| 3. Fault cases are prioritized by safety impact and test feasibility | You will inject high-risk faults first and verify diagnostics. |

| 4. Power electronics behaviour is validated under transient stress | You will find inverter edge cases before hardware trials. |

| 5. Electric machine models reflect thermal and electromagnetic limits | You will tune using motor models that include key limits. |

| 6. Energy storage dynamics are exercised across realistic duty cycles | You will check battery limits and contactor timing under load. |

| 7. Controller interfaces and HIL I/O fidelity are verified early | You will remove scaling and latency errors before tuning. |

| 8. Real-time constraints are verified against worst-case computation load | You will keep step timing stable so results stay trustworthy. |

| 9. Test results map directly to design decisions and release gates | You will link each result to a concrete next action. |

“Real-time performance is mandatory because missed steps can break closed-loop behaviour.”

How to apply this checklist across concept, validation, and release phases

Use the same nine steps at every phase, but tighten pass rules as risk rises. Early work should lock down envelopes, interfaces, and protection. Mid-phase work should add model detail only where it changes control behaviour. Late work should freeze test conditions and focus on gates that must pass every run.

Concept checks can use simplified plants if limits and interfaces stay realistic. Validation work should add stress cases such as torque reversals, sensor faults, and brownouts. Release checks should pin software versions, model versions, and logging settings. Tight control over test conditions stops “it passed last week” arguments.

Discipline matters more than test count, so keep checks that change a decision and cut the rest. When a gate fails, capture the smallest reproduction case and keep it as regression. That habit builds trust because the same run will give the same answer next week. OPAL-RT fits best when it is treated as part of the lab process, with versioned models and recorded settings.

EXata CPS has been specifically designed for real-time performance to allow studies of cyberattacks on power systems through the Communication Network layer of any size and connecting to any number of equipment for HIL and PHIL simulations. This is a discrete event simulation toolkit that considers all the inherent physics-based properties that will affect how the network (either wired or wireless) behaves.